analog circuits Recently Published Documents

Total documents.

- Latest Documents

- Most Cited Documents

- Contributed Authors

- Related Sources

- Related Keywords

Operational transconductance amplifier-based comparator for high frequency applications using 22 nm FinFET technology

<p><span>Fin field-effect transistor (FinFET) based analog circuits are gaining importance over metal oxide semiconductor field effect transistor (MOSFET) based circuits with stability and high frequency operations. Comparator that forms the sub block of most of the analog circuits is designed using operational transconductance amplifier (OTA). The OTA is designed using new design procedures and the comparator circuit is designed integrating the sub circuits with OTA. The building blocks of the comparator design such as input level shifter, differential pair with cascode stage and class AB amplifier for output swing are designed and integrated. Folded cascode circuit is used in the feedback path to maintain the common mode input value to a constant, so that the differential pair amplifies the differential signal. The gain of the comparator is achieved to be greater than 100 dB, with phase margin of 65°, common mode rejection ratio (CMRR) of above 70 dB and output swing from rail to rail. The circuit provides unity gain bandwidth of 5 GHz and is suitable for high sampling rate data converter circuits.</span></p>

A Compact High-Dimensional Yield Analysis Method using Low-Rank Tensor Approximation

“Curse of dimensionality” has become the major challenge for existing high-sigma yield analysis methods. In this article, we develop a meta-model using Low-Rank Tensor Approximation (LRTA) to substitute expensive SPICE simulation. The polynomial degree of our LRTA model grows linearly with the circuit dimension. This makes it especially promising for high-dimensional circuit problems. Our LRTA meta-model is solved efficiently with a robust greedy algorithm and calibrated iteratively with a bootstrap-assisted adaptive sampling method. We also develop a novel global sensitivity analysis approach to generate a reduced LRTA meta-model which is more compact. It further accelerates the procedure of model calibration and yield estimation. Experiments on memory and analog circuits validate that the proposed LRTA method outperforms other state-of-the-art approaches in terms of accuracy and efficiency.

A Native SPICE Implementation of Memristor Models for Simulation of Neuromorphic Analog Signal Processing Circuits

Since the memristor emerged as a programmable analog storage device, it has stimulated research on the design of analog/mixed-signal circuits with the memristor as the enabler of in-memory computation. Due to the difficulty in evaluating the circuit-level nonidealities of both memristors and CMOS devices, SPICE-accuracy simulation tools are necessary for perfecting the art of neuromorphic analog/mixed-signal circuit design. This article is dedicated to a native SPICE implementation of the memristor device models published in the open literature and develops case studies of applying such a circuit simulation with MOSFET models to study how device-level imperfections can make adversarial effects on the analog circuits that implement neuromorphic analog signal processing. Methods on memristor stamping in the framework of modified nodal analysis formulation are presented, and implementation results are reported. Furthermore, functional simulations on neuromorphic signal processing circuits including memristors and CMOS devices are carried out to validate the effectiveness of the native SPICE implementation of memristor models from the perspectives of simulation accuracy, efficiency, and convergence for large-scale simulation tasks.

Remaining Useful Life Prediction of Small and Large Signal Analog Circuits Using Filtering Algorithms

Design principles of 22-nm soi ldd-finfets for ultra-low-power analog circuits, evolutionary synthesis of failure-resilient analog circuits.

Analog circuit design requires large amounts of human knowledge. A special case of circuit design is the synthesis of robust and failure-resilient electronics. Evolutionary algorithms can aid designers in exploring topologies with new properties. Here, we show how to encode a circuit topology with an upper-triangular incident matrix and use the NSGA-II algorithm to find computational circuits that are robust to component failure. Techniques for robustness evaluation and evolutionary algorithm guidances are described. As a result, we evolve square root and natural logarithm computational circuits that are robust to high-impedance or short-circuit malfunction of an arbitrary rectifying diode. We confirm the simulation results by hardware circuit implementation and measurements. We think that our research will inspire further searches for failure-resilient topologies.

Analog Circuit Fault Diagnosis Using a Novel Variant of aConvolutional Neural Network

Analog circuits play an important role in modern electronic systems. Aiming to accurately diagnose the faults of analog circuits, this paper proposes a novel variant of a convolutional neural network, namely, a multi-scale convolutional neural network with a selective kernel (MSCNN-SK). In MSCNN-SK, a multi-scale average difference layer is developed to compute multi-scale average difference sequences, and then these sequences are taken as the input of the model, which enables it to mine potential fault characteristics. In addition, a dynamic convolution kernel selection mechanism is introduced to adaptively adjust the receptive field, so that the feature extraction ability of MSCNN-SK is enhanced. Based on two well-known fault diagnosis circuits, comparison experiments are conducted, and experimental results show that our proposed method achieves higher performance.

Symmetric Coexisting Attractors in a Novel Memristors-Based Chuas Chaotic System

This paper introduces a charge-controlled memristor based on the classical Chuas circuit. It also designs a novel four-dimensional chaotic system and investigates its complex dynamics, including phase portrait, Lyapunov exponent spectrum, bifurcation diagram, equilibrium point, dissipation and stability. The system appears as single-wing, double-wings chaotic attractors and the Lyapunov exponent spectrum of the system is symmetric with respect to the initial value. In addition, symmetric and asymmetric coexisting attractors are generated by changing the initial value and parameters. The findings indicate that the circuit system is equipped with excellent multi-stability. Finally, the circuit is implemented in Field Programmable Gate Array (FPGA) and analog circuits.

A Novel Feature Extraction Method for Soft Faults in Nonlinear Analog Circuits Based on LMD-GFD and KPCA

Brain-inspired hardware solutions for inference in bayesian networks.

The implementation of inference (i.e., computing posterior probabilities) in Bayesian networks using a conventional computing paradigm turns out to be inefficient in terms of energy, time, and space, due to the substantial resources required by floating-point operations. A departure from conventional computing systems to make use of the high parallelism of Bayesian inference has attracted recent attention, particularly in the hardware implementation of Bayesian networks. These efforts lead to several implementations ranging from digital circuits, mixed-signal circuits, to analog circuits by leveraging new emerging nonvolatile devices. Several stochastic computing architectures using Bayesian stochastic variables have been proposed, from FPGA-like architectures to brain-inspired architectures such as crossbar arrays. This comprehensive review paper discusses different hardware implementations of Bayesian networks considering different devices, circuits, and architectures, as well as a more futuristic overview to solve existing hardware implementation problems.

Export Citation Format

Share document.

Thank you for visiting nature.com. You are using a browser version with limited support for CSS. To obtain the best experience, we recommend you use a more up to date browser (or turn off compatibility mode in Internet Explorer). In the meantime, to ensure continued support, we are displaying the site without styles and JavaScript.

- View all journals

- My Account Login

- Explore content

- About the journal

- Publish with us

- Sign up for alerts

- Open access

- Published: 16 July 2020

Low-voltage 2D materials-based printed field-effect transistors for integrated digital and analog electronics on paper

- Silvia Conti ORCID: orcid.org/0000-0002-0294-7551 1 na1 ,

- Lorenzo Pimpolari 1 na1 ,

- Gabriele Calabrese ORCID: orcid.org/0000-0003-0896-0148 1 ,

- Robyn Worsley 2 ,

- Subimal Majee 2 ,

- Dmitry K. Polyushkin 3 ,

- Matthias Paur 3 ,

- Simona Pace ORCID: orcid.org/0000-0002-3947-0136 4 , 5 ,

- Dong Hoon Keum 4 , 5 ,

- Filippo Fabbri 4 , 6 ,

- Giuseppe Iannaccone 1 ,

- Massimo Macucci 1 ,

- Camilla Coletti ORCID: orcid.org/0000-0002-8134-7633 4 , 5 ,

- Thomas Mueller 3 ,

- Cinzia Casiraghi 2 &

- Gianluca Fiori 1

Nature Communications volume 11 , Article number: 3566 ( 2020 ) Cite this article

14k Accesses

118 Citations

6 Altmetric

Metrics details

- Electrical and electronic engineering

- Electronic devices

- Two-dimensional materials

Paper is the ideal substrate for the development of flexible and environmentally sustainable ubiquitous electronic systems, which, combined with two-dimensional materials, could be exploited in many Internet-of-Things applications, ranging from wearable electronics to smart packaging. Here we report high-performance MoS 2 field-effect transistors on paper fabricated with a “channel array” approach, combining the advantages of two large-area techniques: chemical vapor deposition and inkjet-printing. The first allows the pre-deposition of a pattern of MoS 2 ; the second, the printing of dielectric layers, contacts, and connections to complete transistors and circuits fabrication. Average I ON /I OFF of 8 × 10 3 (up to 5 × 10 4 ) and mobility of 5.5 cm 2 V −1 s −1 (up to 26 cm 2 V −1 s −1 ) are obtained. Fully functional integrated circuits of digital and analog building blocks, such as logic gates and current mirrors, are demonstrated, highlighting the potential of this approach for ubiquitous electronics on paper.

Similar content being viewed by others

3D integration of 2D electronics

Selenium alloyed tellurium oxide for amorphous p-channel transistors

On-device phase engineering

Introduction.

In recent years, electronics has witnessed impressive technological achievements, owing to the development of new processes and materials with extraordinary electrical and mechanical properties, which have enabled the development of Internet of Things applications, ranging from wearable electronics to mobile healthcare. This has led to a continuous and marked increase in demand of light-weight, flexible, and low-cost devices, posing strong constrains on traditional fabrication methods 1 , 2 . In addition, this type of pervasive and versatile electronics had led to further concerns on sustainability, such as the treatment of waste at the end of the product life-cycle. Derived from abundant and renewable raw materials, paper-based consumer electronics is expected to alleviate landfill and environmental problems and to reduce the impact associated with recycling operations, whilst offering cost-effectiveness and large flexibility 3 . Despite the fact that several devices and applications have been reported in the literature 4 , paper is still a challenging substrate for electronics, rarely employed without the addition of coating/laminating layers 5 , 6 . Its porous structure (which in turn leads to high roughness), limited stability and durability (mainly due poor thermal and humidity resistance), and high hygroscopicity (which can influence the electrical characterization of devices fabricated on top of it), combined with the lack of winning reliable fabrication techniques, is preventing its exploitation at the industrial level 7 , 8 .

Two-dimensional materials (2DMs) combine good tunable electronic properties with high mechanical flexibility, making them extremely promising as building blocks for flexible electronics 9 , 10 . Moreover, they can be easily produced in solution with mass scalable and low-cost techniques, such as liquid-phase exfoliation 11 , enabling their deposition by simple fabrication techniques such as inkjet printing 12 , 13 , 14 , 15 , 16 , 17 . 2D semiconducting materials, such as transition metal dichalcogenides (TMDCs) 18 , 19 , with extended bandgap tunability through composition, thickness, and possibly even strain control, represent promising materials as channels for field-effect transistors (FETs), which are fundamental components in electronics. However, up to now, fully printed TMDC-based transistors have demonstrated limited performance, showing mobility of the order of under 0.5 cm 2 V −1 s −1 and I ON / I OFF ratios of hundreds, using liquid electrolytes as insulating layers 20 , 21 . Among the various TMDCs, molybdenum disulfide (MoS 2 ) has been widely studied, owing to its outstanding electrical and optical properties 22 , 23 , 24 , 25 , 26 . Lin et al. 27 reported FETs made with solution-processed MoS 2 , showing remarkable performance (average mobility of ~7–11 cm 2 V −1 s −1 ), but device fabrication required acid cleaning and annealing above 200 °C, which are incompatible with substrates such as paper. A large mobility of 19 cm 2 V −1 s −1 for a MoS 2 /graphene transistor was reported in ref. 28 : graphene allows increasing carrier mobility, but this negatively affects the I ON / I OFF ratio.

We combine chemical vapor deposition (CVD), for the growth of high-quality MoS 2 channels, with inkjet printing 29 , 30 , which allows to design and fabricate customizable devices and circuits exploiting 2DMs-based inks, whose capability to be printed on top of CVD-grown materials has been successfully demonstrated in ref. 16 . In this work, an application-specific integrated circuit design approach, known as “channel array”, is proposed: this is based on the transfer of strips of CVD-grown MoS 2 , onto paper substrate where the rest of the devices and circuits, source and drain contacts (which define the effective channel length and width), gate dielectric, gate contacts, and connections, are fully customized exploiting inkjet printing technique, giving a degree of freedom to the designer. This method allows to keep the flexibility and versatility of an all-inkjet technology, with the difference that here a high-quality channel is already placed on the substrate, by taking advantage of the CVD-grown TMDC. Moreover, as both methods are compatible with large-area fabrication processes, their combination could open a possible exploitation at the industrial level.

The MoS 2 FETs fabricated with the channel array method operate at supply voltage below 2 V, with remarkable transistor performance, such as an average field-effect mobility of 5.5 cm 2 V −1 s −1 (with best performance reaching 26 cm 2 V −1 s −1 ), negligible leakage currents (smaller than 5 nA), and an average I ON / I OFF ratio of 8 × 10 3 (up to 5 × 10 4 ). We further exploit the possibility to produce high-performance transistors with the channel array method by demonstrating more complex circuits, such as logic gates (such as NOT and NAND) and analog circuits. This paves the way towards the introduction of the channel array approach in all applications where flexible and/or disposable electronics is required.

Fabrication of MoS 2 FETs on paper

The rationale of our approach is the combination of two fabrication techniques, which up to now have been used for very different applications, to have high-quality semiconducting substrates easily customizable to obtain devices and circuits with a versatile printing technique. The advantage of inkjet-printing is the fast prototyping, which allows for on-the-fly corrections as well as easy pattern changes, simplifying the manufacturing process. Moreover, being an additive and mask-less method, it also cuts down materials and energy consumption, reducing the number of processing steps, time, space, and waste production during the fabrication. On the other hand, inkjet-printing presents critical aspects, such as the need to use inks with specific rheological properties, and, more importantly, the current lack of semiconducting 2DM-based inks for high-performance FETs. Even if expensive, lacking in compatibility with arbitrary substrates, suffering from atomic vacancies and batch-to-batch variations, CVD is, so far, the most-promising bottom–up approach to obtain high-quality semiconducting layer and may become the method of choice, also considering the recent progress in the CVD growth of MoS 2 involving a low-cost, large-area roll-to-roll approach 31 .

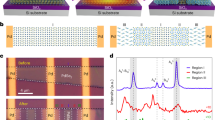

Figure 1a illustrates the procedure followed to pattern CVD MoS 2 and its transfer to paper substrate (a detailed description of the process is reported in Methods, an alternative method for CVD growth and transfer is presented in Supplementary Note 1 ). After the transfer, the polystyrene carrier film is dissolved in toluene, resulting in MoS 2 strips on paper, as shown in Fig. 1b (an atomic force microscopy micrograph of the MoS 2 film on the sapphire substrate before the transfer is reported in Supplementary Note 2 ).

a Schematic representation of the patterning and transferring procedure employed to obtain MoS 2 strips on paper. b Optical micrograph showing the transferred MoS 2 strips on paper. The scale bar corresponds to 1 mm. c Raman spectra acquired on the as-grown MoS 2 layer on rigid substrate (red line) and after MoS 2 transfer to paper (cyan line). d – f Fabrication steps of the inkjet-printed transistors on paper: d Inkjet-printing of silver source and drain contacts. e Inkjet-printing of the hBN dielectric layer (defined by the blue-dotted frame). f Inkjet printing of silver top-gate contact. The scale bars in d – f correspond to 250 μm. g Sketch showing an inkjet-printed circuit on paper with CVD-grown MoS 2 channel.

To evaluate the crystalline quality of the MoS 2 before and after the transfer process from the rigid substrate to the paper, Raman spectroscopy is employed. Figure 1c shows the Raman spectra before (red line) and after (cyan line) the transfer. The red spectrum presents the E 2g and A 1g modes at 383 cm −1 and at 403 cm −1 of single-layer MoS 2 , representative of the in-plane and out-of-plane vibrations of S–Mo–S, respectively 32 . After the transfer process, the MoS 2 Raman modes appear slightly shifted and broadened, i.e., the E 2g and A 1g modes peak at 380 cm −1 and at 400 cm −1 , respectively. As previously reported in ref. 33 , the softening of Raman modes can be attributed to uniaxial strain, albeit the E 2g mode should suffer a larger shift compared with the A 1g mode. In our case, the softening of the Raman modes is comparable, ruling out any strain effect on the MoS 2. Therefore, we argue that the softening is mainly owing to heating effects related to the poor heat dissipation of the paper substrate. This hypothesis is also supported by the broadening of the full-width-at-half-maximum (FWHM) of both modes. Indeed, the E 2g FWHM increases from ~3 cm −1 , before transfer, up to ~7 cm −1 after the transfer process. In the case of the A 1g mode, the broadening is less evident, with the FWHM increasing from ~4 cm −1 up to ~6 cm −1 .

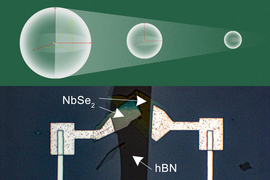

Figure 1d–f show the fabrication of inkjet-printed MoS 2 FETs on paper. First, the source and drain contacts are printed on a MoS 2 stripe to define the channel area of the transistor (Fig. 1d ). Second, a hexagonal boron nitride (hBN) film is printed on the MoS 2 channel (Fig. 1e ). This 2D insulating material is chosen because of its notable dielectric properties and negligible leakage current 15 , 20 , 34 , 35 . Finally, a top-gate electrode is printed on top of hBN (Fig. 1f ). Either silver or graphene inks have been used to print the source and drain contacts as well as the top-gate contacts. The FETs are then connected to each other using the routes defined between the MoS 2 strips, to create the integrated circuit in an efficient and versatile way. This approach is qualitatively described in Fig. 1g .

Electrical characterization of MoS 2 FETs

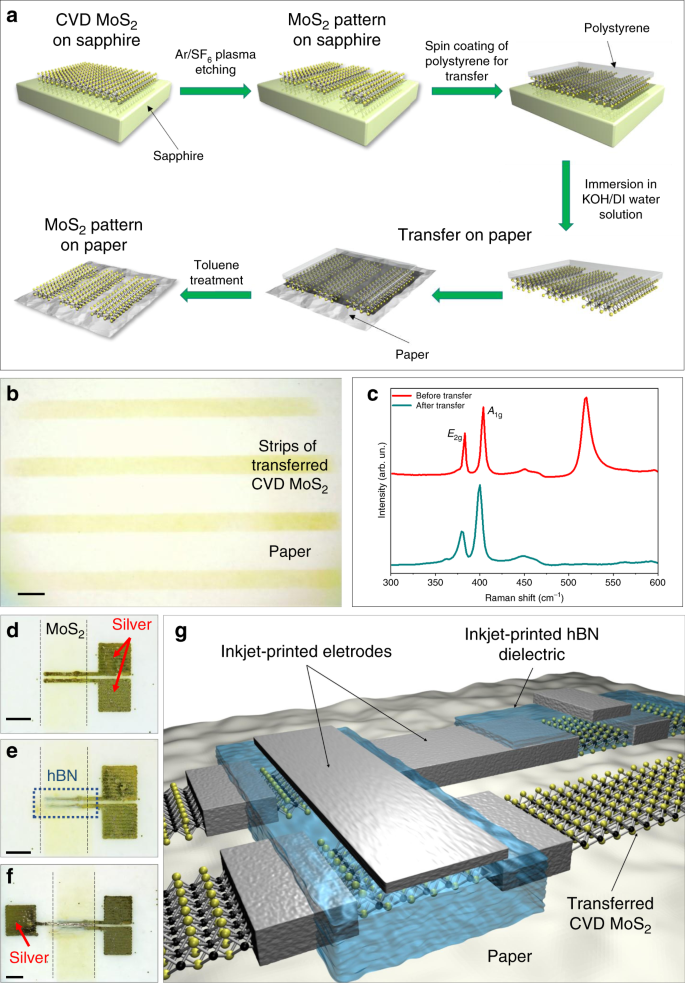

At first, a commercial silver ink (see Methods) was chosen to print the electrodes, because it can assure very high conductivity with just one printing pass, and it has shown ohmic contact with MoS 2 29 . Typical transfer and output characteristics of the MoS 2 FETs are reported in Fig. 2a, c . The devices work in the enhancement mode, can operate at low supply voltage (<2 V), and exhibit a threshold voltage ( V TH ) in the range of ±1 V (see Supplementary Fig. 7c and Supplementary Fig. 7e ). As can be seen, the leakage current I GS (red dots, Fig. 2a ) through the insulator is negligible as compared to the drain current I DS (black dots, logarithmic scale, Fig. 2a ; black dots, linear scale, Fig. 2b ), further confirming the good insulating properties of the inkjet-printed hBN film. The saturation regime is reached for low drain-to-source voltage ( V DS ), i.e., V DS < 2 V. Almost negligible contact resistance is shown from the output characteristic. Indeed, as can be seen from the log–log plot (Fig. 2d ), the linearity parameter γ , describing the relation \(I_{{\mathrm{DS}}} \propto V_{{\mathrm{DS}}}^\gamma\) , is found to be 1.1 on average, indicating a good contact between the CVD MoS 2 and the inkjet-printed silver electrodes.

a Typical transfer characteristic curve measured as a function of the gate voltage for a drain voltage of 2.0 V. Logarithmic scale: black dots, drain current; red dots, gate current. b Typical transfer characteristic curve measured as a function of the gate voltage for a drain voltage of 2.0 V in linear scale. c Typical output characteristic measured at different gate voltages (from V GS = 0.0 V to V GS = 1.75 V, steps of 0.25 V). d Log–log curves of the output characteristic in low drain voltage region. Ohmic behavior is observed, suggesting good electrical contact between the silver contacts and MoS 2 . e Field-effect mobility and ( I ON / I OFF )/ V DD for FETs characterized on paper substrates previously reported in the literature. V DD is the supply voltage for each device. Blue stars, this work, inkjet-printed silver contacts; purple star, this work, inkjet-printed graphene contacts; black dots, 2D materials (25, 28, 43); red dots, organic semiconductors (44, 45, 46, 47, 48, 49, 50); yellow dots, inorganic oxides (51, 52, 53, 54, 55); green dots, CNTs (56, 57). f Transfer characteristics and gate leakage currents measured for different bending radii along the current direction for a drain voltage of 2 V; inset, picture of a sample with MoS 2 FET fabricated on paper.

Charge carrier field-effect mobility ( µ FE ) is one of the most important figures of merit defining the quality of transistor electrical performance. It can be extrapolated using the classical model for devices operating in the saturation regime ( V DS > V GS − V TH ):

where C i is the capacitance of the insulator per unit area, W and L are the transistor channel width and length, respectively, and V GS is the gate voltage. As suggested in ref. 8 , in order to avoid any mobility overestimation, the capacitance was measured under quasi-static conditions (details about the quasi-static capacitance measurement and setup are reported in Supplementary Note 3 ). To this purpose, parallel plate capacitor structures, in which hBN is sandwiched between silver bottom/top electrodes were fabricated and tested (see Methods). The extracted average value of 230 nF cm 2 is in line with other quasi-static measurement performed on both organic and hybrid materials 8 , 36 , 37 , 38 . Thanks to the high capacitive coupling, which results in an enhanced polarization and leads to a high number of carriers at the insulator-semiconductor interface, the devices show an average charge carrier mobility of 5.5 cm 2 V −1 s −1 and I ON / I OFF ratio of 8 × 10 3 . I ON is computed for I DS extracted for gate voltage V GS = V GSoff + V DD and drain voltage V DS = V DD , where V DD is the supply voltage, and V GSoff is the gate voltage for the lowest current flowing in the device, i.e., the OFF current I OFF 39 . The detailed electrical characterization is reported in Supplementary Figs. 2 and 3 . Remarkably, this mobility value is comparable to already reported CVD-grown MoS 2 transistors fabricated on rigid substrates using standard microelectronic fabrication techniques 40 , 41 , 42 , confirming that our methodology, based on the channel array, allows to use inkjet-printing for the fabrication of the devices, without affecting the electronic properties of the channel.

Figure 2e shows µ FE and the normalized I ON / I OFF ratio for our devices compared with those previously reported in the literature: the closer the points to the top-right corner, the better the performance. We considered only transistors fully fabricated on paper or transferred on paper after fabrication. For a fair comparison, all the I ON / I OFF values are re-calculated considering the International Technology Roadmap for Semiconductors definition 39 , and then divided by the respective supply voltage V DD . This normalization allows to take into account the operating voltage ranges of the considered FETs, which is a crucial problem for portable applications, where low power consumption is often required. They have been divided into four groups according to the nature of the semiconductor used as channel: 2D materials 25 , 28 , 43 organic semiconductors 44 , 45 , 46 , 47 , 48 , 49 , 50 , inorganic oxide semiconductors 51 , 52 , 53 , 54 , 55 , carbon nanotubes 56 , 57 . Our devices show competitive electrical performance and are the only one, where both the contacts and the insulating layers are deposited by means of inkjet printing (for a detailed comparison see Supplementary Data 1 ). While maintaining a high I ON / I OFF ratio, the mobility values extracted from the MoS 2 FETs are larger than those obtained for organic semiconductors. Transistors that show comparable or better performance than those presented in this work, as reported in refs. 25 , 51 , 53 , 55 , were fabricated using micro-fabrication techniques for the deposition of insulator and contact layers, as well. It is worth mentioning, that the mobility extracted in this work is comparable to the one found for CVD MoS 2 FETs entirely fabricated using conventional microelectronic techniques on planarized paper substrates 25 . Note that the type of paper used in the literature may be different, and this may affect the performance of the devices and the reproducibility, hence comparison should be done carefully. In some cases, planarization layers were introduced to mitigate the surface roughness of the paper substrates and high-temperature processes were employed, thus increasing the complexity of the transistor manufacturing. In our work, the fabrication process and the electrical characterization are carried out at ambient condition on a commercially available paper, designed for printed electronics (see Supplementary Note 6) that cannot withstand temperatures over 120 °C. The potentiality of our approach stands in the coherent combination of two large-area fabrication processes in order to obtain good electrical performances. In Supplementary Note 5 and Supplementary Data 2 , a comparison with devices fabricated on flexible substrates (other than paper) is reported. As can be seen, our devices are comparable with the best-in-class presented devices.

In order to confirm the compatibility of our technology with flexible substrates, the electromechanical properties of the devices are investigated for various bending radii (R) (more details can be found in Supplementary Note 4.1 ). Figure 2f shows transfer characteristics recorded for R values of 32, 20, 12, and 8 mm. No relevant changes both in the drain and the gate currents are observed, indicating that the device electrical performance is not affected under the applied strain conditions.

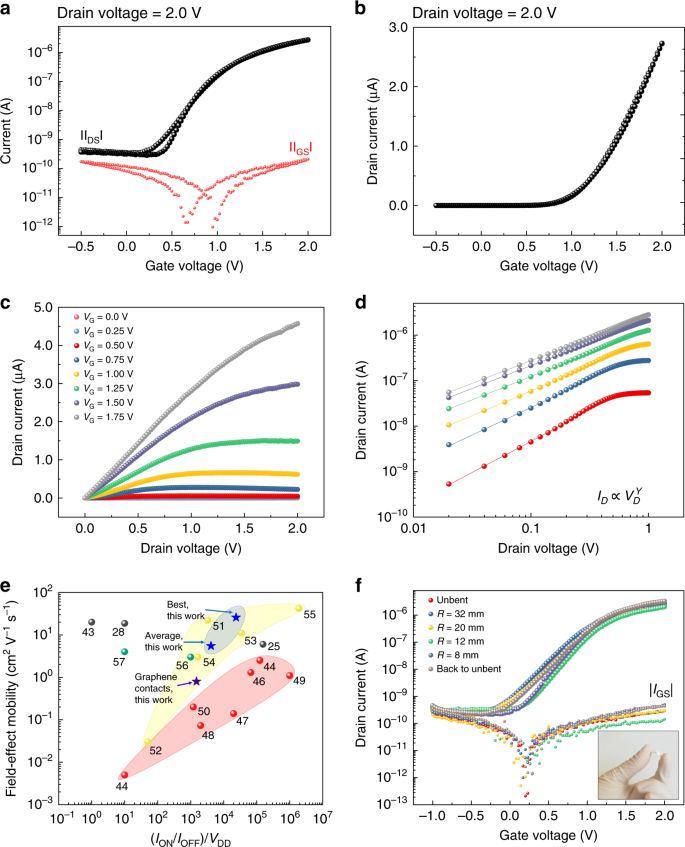

We have then focused on the fabrication of fully 2D-material-based transistors with inkjet-printed graphene source, drain, and gate contacts (see Methods). An optical micrograph of a fully 2D-material-based FET is shown in Fig. 3a , whereas Fig. 3b, c report typical transfer and output characteristic, respectively. These transistors show a reduced effective μ FE (~0.8 cm 2 V −1 s −1 ), and an I ON / I OFF ratio about one order of magnitude smaller (~3 × 10 3 ), compared with transistors with silver contacts (Fig. 2e ). The reduced performance is likely related to the formation of Schottky contacts, which in turn increases the contact resistance, as evident from Fig. 3c , where non-linear behavior of the output characteristic can be observed for small V DS . However, it is remarkable that the extracted field-effect mobility is only six times smaller than the one obtained for a thin film transistor with exfoliated MoS 2 channel and CVD‐grown graphene source/drain electrodes (4.5 cm 2 V −1 s −1 ) 58 .

a Optical micrograph of a fully 2D-material-based transistor on paper. The scale bar corresponds to 250 μm. b Typical transfer characteristic curve measured as a function of the gate voltage for a drain voltage of 2.5 V. Logarithmic scale: black dots, drain current; red dots, gate current. inset, Typical transfer characteristic curve measured as a function of the gate voltage for a drain voltage of 2.5 V in linear scale. c Typical output characteristic curves measured at increasing gate voltages (from V GS = 0.0 V to V GS = 1.75 V, steps of 0.25 V).

Integrated circuits on paper

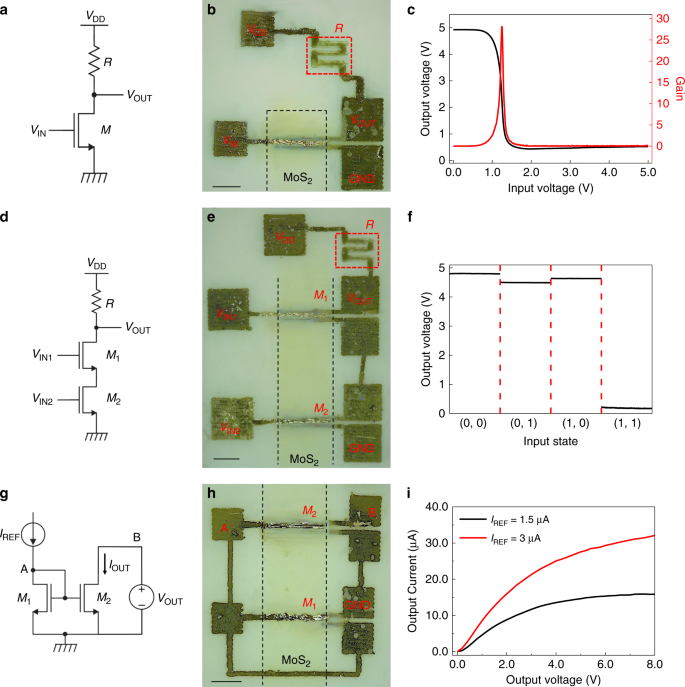

To demonstrate the potential of the fabricated FETs as building blocks for integrated circuits exploiting the channel array technology, different types of circuits have been designed and fabricated. MoS 2 FETs with inkjet-printed silver contacts were selected owing to the high I ON / I OFF ratio, intrinsic gain, and low power supply voltage to fabricate a resistor-transistor logic (RTL) inverter, consisting of a transistor and an inkjet-printed graphene resistor. Figure 4a, b show the schematic and the optical image of a RTL inverter, respectively. The transfer characteristic of an inverter is shown in Fig. 4c (left axis), together with the gain G (right axis), defined as the slope dV OUT / dV IN of the transfer curve (where V IN and V OUT are the input and output voltages, respectively). The inverter exhibits a high-gain value, close to 30 under a voltage bias of 5 V, in agreement with previously reported inverters based on CVD-grown MoS 2 fabricated on rigid substrates 41 , 59 .

a Electrical schematic and b optical image of an inverter. c Output voltage (left axis) and voltage gain (right axis) of the inverter gate as a function of the input voltage. d Electrical schematic and e optical image of a NAND gate. f Output voltage of the NAND gate as a function of the input states ( V IN1 , V IN2 ). Voltage bias is 5 V for both the inverter and the NAND gate. g Electrical schematic and h optical image of a current mirror. i Output current of the current mirror as a function of the output voltage for two different values of the reference current. Legend: V DD , supply voltage; GDN, ground reference; V IN and V OUT , input and output voltage; M , inkjet-printed transistor. R , inkjet-printed graphene resistor. The scale bars in b , e , h correspond to 250 μm.

The schematic and the optical image of a NAND gate are shown in Fig. 4d, e , whereas Fig. 4f shows the output voltage of the circuit as a function of the inputs ( V IN1 , V IN2 ). The low and high logic values of the inputs correspond to voltages of 0 V and 5 V, respectively. The output voltage is high (i.e., at logic state “1”) when at least one input is in the logic state “0”, and therefore at least one transistor is in the OFF state. The output voltage is low (i.e., at logic state “0”) only when both inputs are at the logic state “1”: in these conditions both transistors are in the ON state. The possibility to implement NAND gates is particularly important, as all other logic functions can be implemented using NAND gates.

As a further demonstration of the potential of the presented technology, we propose an application for analog electronics. Current mirrors are fundamental building blocks in analog electronic circuits, where they are widely used for operational amplifiers, bandgap voltage reference, etc. 60 , and they can also be exploited in neural networks, in order to implement matrix-vector multiplication 61 . Figure 4g, h show the schematic and the optical image of the fabricated current mirror. The output transistor (M 2 ) is 10 times wider than the input transistor (M 1 ), whereas all the other transistor parameters are identical; therefore, the current mirror has a nominal gain of 10. Figure 4i shows the current mirror output characteristic, i.e., the output current as a function of the output voltage, for two different values of the input reference current. As shown in the plot, for sufficiently high output voltages (i.e., M 2 in saturation) the output current is about 10 times larger than the reference current ( I REF ), in accordance with the circuit design.

We have successfully demonstrated high-performance MoS 2 -based transistors that combine the numerous advantages of using paper as a substrate with the versatility of inkjet-printing technique, whilst maintaining the good electrical properties of CVD-grown MoS 2 . A maximum field-effect mobility of 26 cm 2 V −1 s −1 and an I ON / I OFF ratio of up to 5 × 10 4 were achieved. Bending tests have shown that the device electrical properties are robust under applied strain (up to a bending radius of 8 mm). Moreover, our device fabrication approach has been proven to be suitable for the development of complete integrated circuits, such as high-gain inverters, logic gates, and current mirrors. This work demonstrates the great potential of the channel array technology for next-generation electronics on paper, ranging from analogic to digital circuits for cost-efficient and practical applications.

PEL P60 (purchased from Printed Electronics Limited) is used as paper substrate (more details can be found in Supplementary Note 6 ). A commercial silver ink (Sigma-Aldrich) is used to print the metal contacts. Bulk graphite (purchased from Graphexel or Sigma-Aldrich, 99.5% grade) and bulk boron nitride (purchased from Sigma-Aldrich, >1 μm, 98% grade) powders were used to prepare the 2DMs inks. The bulk powders are dispersed in deionized water (resistivity 18.2 MΩ cm −1 ) at a concentration of 3 mg mL −1 and 1-pyrenesulphonic acid sodium salt (PS1, purchased from Sigma-Aldrich), purity ≥97%, is added at a concentration of 1 mg mL −1 . The graphite and boron nitride dispersions are then sonicated for 72 h and 120 h, respectively, using a 300 W Hilsonic HS 1900/Hilsonic FMG 600 bath sonicator at 20 °C. The resultant dispersions is centrifuged at 3500 rpm ( g factor = 903) for 20 minutes at 20 °C using a Sigma 1–14 K refrigerated centrifuge in order to separate out and discard the residual bulk, non-exfoliated flakes. The remaining supernatant, now containing the correct flake size and monolayer percentage, is centrifuged twice to remove excess PS1 from the dispersion. After washing, the precipitate is re-dispersed in the printing solvent, made as described in ref. 16 . The concentration of the resultant inks are assessed using a Varian Cary 5000 UV-Vis spectrometer and the Lambert-Beer law, with extinction coefficients of 2460 (at 660 nm) and 1000 L g −1 m −1 (at 550 nm) for graphene 11 and hBN 62 , respectively. Full characterization of the material (lateral size and thickness distribution, crystallinity, etc.) has been presented in refs. 16 , 34 , 63 .

Growth of MoS 2 and transfer on paper

Single- and few-layer MoS 2 have been grown by CVD on c-plane sapphire 64 . CVD growth is performed at atmospheric pressure using ultra-high-purity Ar as the carrier gas. The substrates are placed face-down 15 mm above a crucible containing ∼ 3 mg of MoO 3 (99.998% Alfa Aesar) and loaded into a split-tube two-zone CVD furnace with a 30 mm outer diameter quartz tube. A second crucible containing 1 g of sulfur (99.9% purity, Sigma-Aldrich) is loaded upstream from the growth substrates and heated to 140 °C. Just before starting the growth, the tube is flushed with Ar at room temperature and atmospheric pressure. The furnace is pre-heated to 750 °C for few hours for temperature stabilization. The substrate and MoO 3 precursor were then loaded into the growth area of the furnace to start the growth. Ar is supplied with a flow of 10 sscm. After 10 min growth at 750 °C, the furnace is left to cool naturally. The synthesized MoS 2 film is transferred from the native sapphire substrate to the paper substrates 65 . Prior to the film transfer, MoS 2 is patterned to obtain a stripped structure on the growth substrate. The pattern is defined by means of Ar/SF 6 plasma etching in an Oxford Cobra Reactive Ion Etching system. The etch mask is created by optical lithography using AZ 5214E photoresist. A 5% KOH solution in DI water is employed to remove the etch mask. The sample is then rinsed in DI water for several times to remove the KOH remnants. To transfer the patterned film, the sapphire substrate with the MoS 2 layer film is first covered with a polystyrene film by spin coating a solution of polystyrene in toluene onto the substrate, which is then immersed in DI water. To facilitate the lift-off process, a solution of KOH in DI water is also added for a short time. After that, the carrier polystyrene film with the MoS 2 layer is rinsed for several times in DI water. To remove the absorbed water the polymeric film is dried at 50 °C in dry air atmosphere and then transferred onto the paper substrate. To improve the adhesion between the carrier polymer film and the wafer the sample is baked at 150 °C for about an hour. The polystyrene carrier film is then dissolved in toluene resulting in a MoS 2 film on paper. Raman characterization before and after transfer has been performed with a Renishaw InVia spectrometer equipped with a confocal optical microscope and a 532 nm excitation laser. The spectral resolution of the system is 1 cm −1 . Raman experiments were carried out employing a ×50 objective (N.A. 0.6), laser power of 5 mW and an acquisition time of 2 s. The pixel size is 1 µm × 1 µm.

Devices fabrication

MoS 2 transistors are fabricated in a top-gate/top-contact configuration on the CVD MoS 2 stripes transferred on paper. A Dimatix Materials Printer 2850 (Fujifilm) is used to define the contacts and the insulator layers under ambient conditions. It is worth underlining that no annealing or post-treatment process is performed after any printing step. The silver ink is deposited with a single printing pass using one nozzle, a drop spacing of 40 μm, and keeping the printer platen at room temperature. Cartridges with a typical droplet volume of 1 pL are used for the definition of the contacts. When the 2.5 mg ml −1 graphene ink is employed, source and drain contacts are inkjet-printed using a drop spacing of 20 μm, and 20 printing passes. Cartridges with a droplet volume of 10 pL are used for the definition of the graphene contacts. For the top-gate contacts, only six printing passes of graphene ink at the same concentration are used in order to reduce the possibility of overlapping with the source and drain contacts (which would significantly increase the leakage current) at each print pass. A ~2 mg/mL hBN ink is printed on top of the CVD-grown MoS 2 using a drop spacing of 20 μm and 80 printing passes. Cartridges with a droplet volume of 10 pL are used for the definition of the insulating layer. Several transistors have been fabricated (with a yield of around 80%) and characterized with a nominal width of ~500 μm and length varying between 40 μm and 60 μm (further details can be found Supplementary Table 1 ).

Parallel plate capacitors with silver/graphene bottom/top electrodes are also printed on paper to evaluate the capacitance of the hBN layers. The inks and the fabrication procedures are kept the same for all the reported devices.

Electrical characterization

All the electrical measurements are performed under ambient conditions. The transistor characterization is carried out using a Keithley SCS4200 parameter analyzer. Capacitance measurements are performed with an R&SRTO2014 oscilloscope and a HP 33120A function/arbitrary waveform generator. The detailed description of the measurement setup can be found in the Supplementary Information .

Data availability

The data that support the findings of this work are available from the corresponding authors upon reasonable request.

Huang, S., Liu, Y., Zhao, Y., Ren, Z. & Guo, C. F. Flexible electronics: stretchable electrodes and their future. Adv. Funct. Mater. 29 , 1805924 (2019).

Google Scholar

Wang, C. et al. Advanced carbon for flexible and wearable electronics. Adv. Mater. 31 , 1801072 (2019).

Tobjörk, D. & Österbacka, R. Paper electronics. Adv. Mater. 23 , 1935–1961 (2011).

PubMed Google Scholar

Ha, D., Fang, Z. & Zhitenev, N. B. Paper in electronic and optoelectronic devices. Adv. Electron. Mater. 4 , 1–20 (2018).

Lessing, J. et al. Inkjet printing of conductive inks with high lateral resolution on omniphobic ‘rF paper’ for paper-based electronics and MEMS. Adv. Mater. 26 , 4677–4682 (2014).

CAS PubMed Google Scholar

Brunetti, F. et al. Printed solar cells and energy storage devices on paper substrates. Adv. Funct. Mater . 29 , 1806798 (2019).

Zhang, Y. et al. Flexible electronics based on micro/nanostructured paper. Adv. Mater. 30 , 1801588 (2018).

Zschieschang, U. & Klauk, H. Organic transistors on paper: a brief review. J. Mater. Chem. C. 7 , 5522–5533 (2019).

CAS Google Scholar

Akinwande, D., Petrone, N. & Hone, J. Two-dimensional flexible nanoelectronics. Nat. Commun. 5 , 5678 (2014).

ADS CAS PubMed Google Scholar

Franklin, A. D. Nanomaterials in transistors: from high-performance to thin-film applications. Science 349 , aab2750-1–aab2750-9 (2015).

Hernandez, Y. et al. High-yield production of graphene by liquid-phase exfoliation of graphite. Nat. Nanotechnol. 3 , 563–568 (2008).

Torrisi, F. et al. Inkjet-printed graphene electronics. ACS Nano 6 , 2992–3006 (2012).

Finn, D. J. et al. Inkjet deposition of liquid-exfoliated graphene and MoS 2 nanosheets for printed device applications. J. Mater. Chem. C. 2 , 925–932 (2014).

Withers, F. et al. Heterostructures produced from nanosheet-based inks. Nano Lett. 14 , 3987–3992 (2014).

Carey, T. et al. Fully inkjet-printed two-dimensional material field-effect heterojunctions for wearable and textile electronics. Nat. Commun. 8 , 1202 (2017).

ADS PubMed PubMed Central Google Scholar

McManus, D. et al. Water-based and biocompatible 2D crystal inks for all-inkjet-printed heterostructures. Nat. Nanotechnol. 12 , 343–350 (2017).

Hu, G. et al. Functional inks and printing of two-dimensional materials. Chem. Soc. Rev. 47 , 3265–3300 (2018).

Manzeli, S., Ovchinnikov, D., Pasquier, D., Yazyev, O. V. & Kis, A. 2D transition metal dichalcogenides. Nat. Rev. Mater. 2 , 17033 (2017).

ADS CAS Google Scholar

Gong, Y., Carozo, V., Li, H., Terrones, M. & Jackson, T. N. High flex cycle testing of CVD monolayer WS 2 TFTs on thin flexible polyimide. 2D Mater. 3 , 0–6 (2016).

Kelly, A. G. et al. All-printed thin-film transistors from networks of liquid-exfoliated nanosheets. Science 356 , 69–73 (2017).

Kelly, A. G., Vega-Mayoral, V., Boland, J. B. & Coleman, J. N. Whiskey-phase exfoliation: exfoliation and printing of nanosheets using Irish whiskey. 2D Mater. 6 , 045036 (2019).

Radisavljevic, B., Radenovic, A., Brivio, J., Giacometti, V. & Kis, A. Single-layer MoS 2 transistors. Nat. Nanotechnol. 6 , 147–150 (2011).

Li, J., Naiini, M. M., Vaziri, S., Lemme, M. C. & Östling, M. Inkjet printing of MoS 2 . Adv. Funct. Mater. 24 , 6524–6531 (2014).

Tong, X., Ashalley, E., Lin, F., Li, H. & Wang, Z. M. Advances in MoS 2 -based field effect transistors (FETs). Nano-Micro Lett. 7 , 203–218 (2015).

Park, S. & Akinwande, D. First demonstration of high performance 2D monolayer transistors on paper substrates. In 2017 IEEE International Electron Devices Meeting (IEDM) 5.2.1–5.2.4 (IEEE, 2017).

Choi, M. et al. Flexible active-matrix organic light-emitting diode display enabled by MoS 2 thin-film transistor. Sci. Adv. 4 , 1–8 (2018).

Lin, Z. et al. Solution-processable 2D semiconductors for high-performance large-area electronics. Nature 562 , 254–258 (2018).

Sahatiya, P. & Badhulika, S. Wireless, smart, human motion monitoring using solution processed fabrication of graphene-Mos 2 transistors on paper. Adv. Electron. Mater. 4 , 1700388 (2018).

Kim, T.-Y. et al. Electrical properties of synthesized large-area MoS 2 field-effect transistors fabricated with inkjet-printed contacts. ACS Nano 10 , 2819–2826 (2016).

Kim, T.-Y. et al. Transparent large-area MoS 2 phototransistors with inkjet-printed components on flexible platforms. ACS Nano 11 , 10273–10280 (2017).

Lim, Y. R. et al. Roll-to-roll production of layer-controlled molybdenum disulfide: a platform for 2D semiconductor-based industrial applications. Adv. Mater. 30 , 1705270 (2018).

Xu, X. et al. High‐performance monolayer MoS 2 films at the wafer scale by two‐step growth. Adv. Funct. Mater. 29 , 1901070 (2019).

Rice, C. et al. Raman-scattering measurements and first-principles calculations of strain-induced phonon shifts in monolayer MoS 2 . Phys. Rev. B 87 , 081307 (2013).

ADS Google Scholar

Worsley, R. et al. All-2D material inkjet-printed capacitors: toward fully printed integrated circuits. ACS Nano 13 , 54–60 (2019).

Lu, S. et al. Flexible, print-in-place 1D–2D thin-film transistors using aerosol jet printing. ACS Nano 13 , 11263–11272 (2019).

Almora, O. et al. Capacitive dark currents, hysteresis, and electrode polarization in lead halide perovskite solar cells. J. Phys. Chem. Lett. 6 , 1645–1652 (2015).

Kong, D. et al. Capacitance characterization of elastomeric dielectrics for applications in intrinsically stretchable thin film transistors. Adv. Funct. Mater. 26 , 4680–4686 (2016).

Dutta, K., Hazra, A. & Bhattacharyya, P. Ti/TiO 2 nanotube array/Ti capacitive device for non-polar aromatic hydrocarbon detection. IEEE Trans. Device Mater. Reliab. 16 , 235–242 (2016).

International Technology Roadmap for Semiconductors–ITRS. Available at: http://www.itrs2.net/ .

Zheng, J. et al. High-mobility multilayered MoS 2 flakes with low contact resistance grown by chemical vapor deposition. Adv. Mater. 29 , 1604540 (2017).

Wachter, S., Polyushkin, D. K., Bethge, O. & Mueller, T. A microprocessor based on a two-dimensional semiconductor. Nat. Commun. 8 , 14948 (2017).

ADS CAS PubMed PubMed Central Google Scholar

Gao, Q. et al. Scalable high performance radio frequency electronics based on large domain bilayer MoS 2 . Nat. Commun. 9 , 4778 (2018).

Veeralingam, S. & Badhulika, S. 2D - SnSe 2 nanoflakes on paper with 1D - NiO gate insulator based MISFET as multifunctional NIR photo switch and flexible temperature sensor. Mater. Sci. Semicond. Process. 105 , 104738 (2020).

Huang, J. et al. Highly transparent and flexible nanopaper transistors. ACS Nano 7 , 2106–2113 (2013).

Minari, T. et al. Room-temperature printing of organic thin-film transistors with π-junction gold nanoparticles. Adv. Funct. Mater. 24 , 4886–4892 (2014).

Fujisaki, Y. et al. Transparent nanopaper-based flexible organic thin-film transistor array. Adv. Funct. Mater. 24 , 1657–1663 (2014).

Hyun, W. J. et al. All-printed, foldable organic thin-film transistors on glassine paper. Adv. Mater. 27 , 7058–7064 (2015).

Dai, S. et al. Intrinsically ionic conductive cellulose nanopapers applied as all solid dielectrics for low voltage organic transistors. Nat. Commun. 9 , 2737 (2018).

Kraft, U. et al. Low-voltage, high-frequency organic transistors and unipolar and complementary ring oscillators on paper. Adv. Electron. Mater. 5 , 1800453 (2019).

Casula, G. et al. Printed, low-voltage, all-organic transistors and complementary circuits on paper substrate. Adv. Electron. Mater. 1901027 , 1–9 (2020).

Martins, R. F. P. et al. Recyclable, flexible, low-power oxide electronics. Adv. Funct. Mater. 23 , 2153–2161 (2013).

Thiemann, S. et al. Cellulose-based ionogels for paper electronics. Adv. Funct. Mater. 24 , 625–634 (2014).

Kim, S. J. et al. Nonvolatile memory thin-film transistors using biodegradable chicken albumen gate insulator and oxide semiconductor channel on eco-friendly paper substrate. ACS Appl. Mater. Interfaces 7 , 4869–4874 (2015).

Gaspar, D. et al. Planar dual‐gate paper/oxide field effect transistors as universal logic gates. Adv. Electron. Mater. 4 , 1800423 (2018).

Wang, X., Gao, Y., Liu, Z., Luo, J. & Wan, Q. Flexible low-voltage IGZO thin-film transistors with polymer electret gate dielectrics on paper substrates. IEEE Electron Device Lett. 40 , 224–227 (2019).

Liu, N., Yun, K. N., Yu, H.-Y., Shim, J. H. & Lee, C. J. High-performance carbon nanotube thin-film transistors on flexible paper substrates. Appl. Phys. Lett. 106 , 103106 (2015).

Yoon, J. et al. Flammable carbon nanotube transistors on a nitrocellulose paper substrate for transient electronics. Nano Res. 10 , 87–96 (2017).

Yoon, J. et al. Highly flexible and transparent multilayer MoS 2 transistors with graphene electrodes. Small 9 , 3295–3300 (2013).

Lan, Y.-W. et al. Scalable fabrication of a complementary logic inverter based on MoS 2 fin-shaped field effect transistors. Nanoscale Horiz. 4 , 683–688 (2019).

Razavi, B. Design of Analog CMOS Integrated Circuits . 2nd edn, 704 (McGraw-Hill Education, 2005).

Wang, Z. et al. Current mirror array: a novel circuit topology for combining physical unclonable function and machine learning. IEEE Trans. Circuits Syst. I Regul. Pap. 65 , 1314–1326 (2018).

Coleman, J. N. et al. Two-dimensional nanosheets produced by liquid exfoliation of layered materials. Science 331 , 568–571 (2011).

Calabrese, G. et al. Inkjet-printed graphene Hall mobility measurements and low-frequency noise characterization. Nanoscale 12 , 6708–6716 (2020).

Dumcenco, D. et al. Large-area epitaxial monolayer MoS 2 . ACS Nano 9 , 4611–4620 (2015).

CAS PubMed PubMed Central Google Scholar

Gurarslan, A. et al. Surface-energy-assisted perfect transfer of centimeter-scale monolayer and few-layer MoS 2 films onto arbitrary substrates. ACS Nano 8 , 11522–11528 (2014).

Download references

Acknowledgements

We acknowledge the ERC PEP2D (contract no. 770047) and H2020 WASP (contract no. 825213) for financial support. C.Ca., C.Co., G.F.,T.M. acknowledge the Graphene Flagship Core 3 (contract no. 881603). R.W. acknowledges the Hewlett-Packard Company for financial support in the framework of the Graphene NOWNANO Centre for Doctoral Training;. C.Ca. acknowledges useful discussions with Alessandro Molle, and financial support from the Grand Challenge EPSRC grant EP/N010345/1. S.P. and C.Co acknowledge financial support from Compagnia di San Paolo (project STRATOS).

Author information

These authors contributed equally: Silvia Conti, Lorenzo Pimpolari.

Authors and Affiliations

Dipartimento di Ingegneria dell’Informazione, University of Pisa, Pisa, 56122, Italy

Silvia Conti, Lorenzo Pimpolari, Gabriele Calabrese, Giuseppe Iannaccone, Massimo Macucci & Gianluca Fiori

Department of Chemistry, University of Manchester, Manchester, M13 9PL, UK

Robyn Worsley, Subimal Majee & Cinzia Casiraghi

Institute of Photonics, Vienna University of Technology, Vienna, 1040, Austria

Dmitry K. Polyushkin, Matthias Paur & Thomas Mueller

Center for Nanotechnology Innovation @NEST, Istituto Italiano di Tecnologia, Pisa, 56127, Italy

Simona Pace, Dong Hoon Keum, Filippo Fabbri & Camilla Coletti

Graphene Labs, Istituto Italiano di Tecnologia, Genova, 16163, Italy

Simona Pace, Dong Hoon Keum & Camilla Coletti

CNR, Scuola Normale Superiore, Pisa, 56127, Italy

Filippo Fabbri

You can also search for this author in PubMed Google Scholar

Contributions

R.W., S.M. developed the inks under the supervision of C.Ca.; D.K.P., M.P., S.P., D.H.K., and F.F. carried out the MoS 2 growth and the transfer on the paper substrates, and performed the Raman spectroscopy and imaging under the supervision of T.M and C.Co.; S.C., L.P., G.C., and G.F. fabricated the electronic devices, performed the electrical measurements, and analyzed the results; G.F, G.I., and M.M. designed and supervised the research. All authors discussed the results and contributed to the manuscript.

Corresponding author

Correspondence to Gianluca Fiori .

Ethics declarations

Competing interests.

The authors declare no competing interests.

Additional information

Peer review information Nature Communications thanks the anonymous reviewers for their contribution to the peer review of this work. Peer review reports are available.

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Supplementary information, descriptions of additional supplementary files, supplementary data 1, supplementary data 2, peer review file, rights and permissions.

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/ .

Reprints and permissions

About this article

Cite this article.

Conti, S., Pimpolari, L., Calabrese, G. et al. Low-voltage 2D materials-based printed field-effect transistors for integrated digital and analog electronics on paper. Nat Commun 11 , 3566 (2020). https://doi.org/10.1038/s41467-020-17297-z

Download citation

Received : 12 November 2019

Accepted : 18 June 2020

Published : 16 July 2020

DOI : https://doi.org/10.1038/s41467-020-17297-z

Share this article

Anyone you share the following link with will be able to read this content:

Sorry, a shareable link is not currently available for this article.

Provided by the Springer Nature SharedIt content-sharing initiative

This article is cited by

The roadmap of 2d materials and devices toward chips.

- Xiaowei Zhang

- Tian-Ling Ren

Nano-Micro Letters (2024)

Van der Waals nanomesh electronics on arbitrary surfaces

- Johnny C. Ho

Nature Communications (2023)

12-inch growth of uniform MoS2 monolayer for integrated circuit manufacture

Nature Materials (2023)

Low power flexible monolayer MoS2 integrated circuits

- Qinqin Wang

- Guangyu Zhang

Printed transistors made of 2D material-based inks

- Silvia Conti

- Gabriele Calabrese

- Gianluca Fiori

Nature Reviews Materials (2023)

By submitting a comment you agree to abide by our Terms and Community Guidelines . If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.

Quick links

- Explore articles by subject

- Guide to authors

- Editorial policies

Sign up for the Nature Briefing newsletter — what matters in science, free to your inbox daily.

An International Journal

Aims and scope

Description

Analog Integrated Circuits and Signal Processing is an archival peer reviewed journal publishing research and tutorial papers on the design and applications of analog, radio frequency (RF) and mixed signal integrated circuits (ICs), and signal processing circuits and systems. It is published monthly with worldwide distribution to engineers, researchers, educators, and libraries.

The journal promotes and expedites the dissemination of new research results and tutorial views. There is an exciting and large volume of research activity in the field worldwide. Engineers and researchers are striving to build complete systems on chip (SoC) by integrating analog and RF circuits in chip fabrication technologies optimized for digital ICs, and to bridge the gap between classical analog work and recent advances in fabrication technologies with improved analog, RF and mixed signal capabilities. As we move to deep nanometer technologies, analog and RF work is showing signs of dramatic changes with emphasis on interdisciplinary research efforts combining device, circuit, technology issues. Consequently, new design concepts, strategies and design tools as well as new applications in wireless and wire line communications, consumer electronics, automotive, control and biomedical systems are being unveiled.

Topics of interest include, but are not limited to:

Analog and Mixed Signal Interface Circuits and Systems; Analog and RFIC Design; Data converters; Active-RC, switched-capacitor and continuous-time integrated filters; Mixed analog/digital VLSI systems; RF Front ends, Frequency Synthesizers, integrated power amplifiers Wireless radio transceivers; Clock and data recovery circuits; Simulation and modeling, mixed-mode simulation; Analog nonlinear circuits and signal processing; Analog Artificial Neural Networks; Design solutions for machine learning; Current mode signal processing circuits and systems; High speed optoelectronics circuits and systems; Power management and energy harvesting solutions; Cyber physical systems; Hardware security solutions; Systems on chip for internet of Things; Analog VLSI cell libraries; Analog and RF product development; Low voltage/low power analog and RFIC design; Microwave and Millimeter wave Circuits; Artificial Intelligence, analog behavioral modeling, Analog HDL; Computer-Aided Design (CAD) tools; Analog Design Automation/Knowledge-based Systems; Analog Design in emerging technologies (nanometer CMOS, SiGe BiCMOS, GaAs, heterojunction and floating gate technologies, etc.); Analog Design for Test; Integrated sensors and actuators

- Find a journal

- Publish with us

- Track your research

Academia.edu no longer supports Internet Explorer.

To browse Academia.edu and the wider internet faster and more securely, please take a few seconds to upgrade your browser .

- We're Hiring!

- Help Center

Analog Electronics

- Most Cited Papers

- Most Downloaded Papers

- Newest Papers

- Save to Library

- Parity Bit Generator usin PTL Design Follow Following

- Analog Circuit Design Follow Following

- CMOS Integrated Circuit Design Follow Following

- Vlsi Design Follow Following

- Electrical Drives Follow Following

- Process Control Follow Following

- Digital Electronics Follow Following

- Operating Systems Follow Following

- Modeling and Simulation Follow Following

- VLSI and Circuit Design Follow Following

Enter the email address you signed up with and we'll email you a reset link.

- Academia.edu Publishing

- We're Hiring!

- Help Center

- Find new research papers in:

- Health Sciences

- Earth Sciences

- Cognitive Science

- Mathematics

- Computer Science

- Academia ©2024

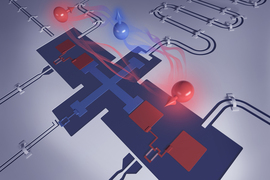

IBM Research's latest analog AI chip for deep learning inference

The energy-efficient chip showcases critical building blocks of a scalable mixed-signal architecture.

We’re just at the beginning of an AI revolution that will redefine how we live and work. In particular, deep neural networks (DNNs) have revolutionized the field of AI and are increasingly gaining prominence with the advent of foundation models and generative AI . But running these models on traditional digital computing architectures limits their achievable performance and energy efficiency. There has been progress in developing hardware specifically for AI inference, but many of these architectures physically split the memory and processing units. This means the AI models are typically stored in a discrete memory location, and computational tasks require constantly shuffling data between the memory and processing units. This process slows down computation and limits the maximum achievable energy efficiency.

IBM Research has been investigating ways to reinvent the way that AI is computed. Analog in-memory computing, or simply analog AI, is a promising approach to address the challenge by borrowing key features of how neural networks run in biological brains. In our brains, and those of many other animals, the strength of synapses (which are the “weights” in this case) determine communication between neurons. For analog AI systems, we store these synaptic weights locally in the conductance values of nanoscale resistive memory devices such as Phase-change memory (PCM) works when an electrical pulse is applied to a material, which changes the conductance of the device. The material switches between amorphous and crystalline phases, where a lower electrical pulse will make the device more crystalline, providing less resistance, and a higher electrical pulse makes the device more amorphous, resulting in more resistance. Instead of recording the usual 0s or 1s you would see in digital systems, the PCM device records its state as a continuum of values between the amorphous and crystalline states. This value is called a synaptic weight, which can be stored in the physical atomic configuration of each PCM. The memory is non-volatile, so the weights are retained when the power supply is switched off. phase-change memory (PCM) and perform multiply-accumulate (MAC) operations, the dominant compute operation in DNNs by exploiting circuit laws and mitigating the need to constantly send data between memory and processor.

To turn the concept of analog AI into a reality, two key challenges need to be overcome: These memory arrays need to be able to compute with a level of precision on par with existing digital systems, and they need to be able to interface seamlessly with other digital compute units, as well as a digital communication fabric on the analog AI chip.

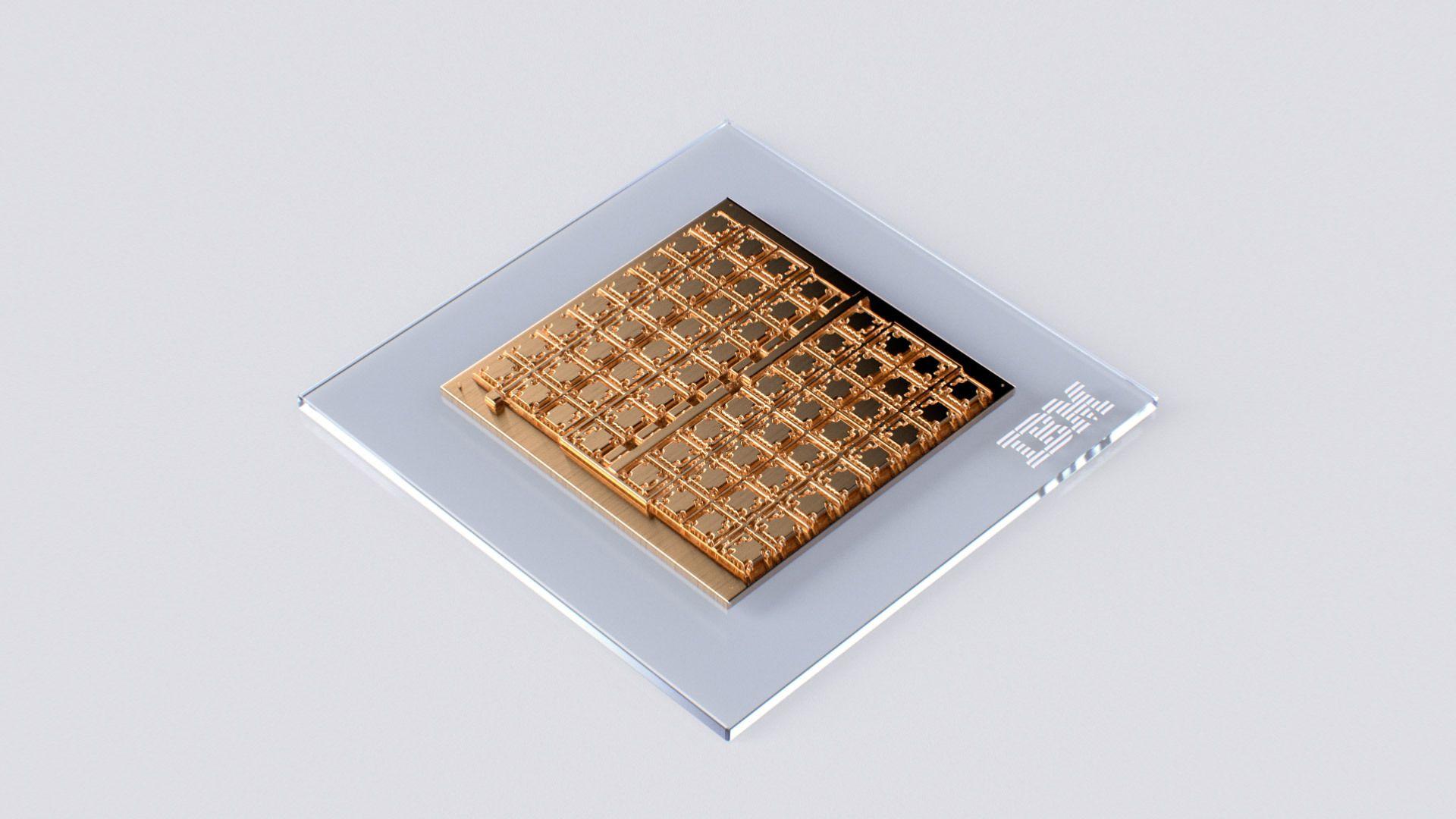

In a paper published today in Nature Electronics , IBM Research made a significant step towards addressing these challenges by introducing a state-of-the-art, mixed-signal analog AI chip for running a variety of DNN inference tasks. It’s the first analog chip that has been tested to be as adept at computer vision AI tasks as digital counterparts, while being considerably more energy efficient.

The chip was fabricated in IBM’s Albany NanoTech Complex , and is composed of 64 analog in-memory compute cores (or tiles), each of which contains 256-by-256 crossbar array of synaptic unit cells. Compact, time-based analog-to-digital converters are integrated in each tile to transition between the analog and digital worlds. Each tile is also integrated with lightweight digital processing units that perform simple nonlinear neuronal activation functions and scaling operations.

Each tile can perform the computations associated with a layer of a DNN model. The synaptic weights are encoded as analog conductance values of the PCM devices. A global digital processing unit is integrated in the middle of the chip that implements more complex operations that are critical for the execution of certain types of neural networks. The chip also has digital communication pathways at the chip interconnects of all the tiles and the global digital processing unit.

Using the chip, we performed the most comprehensive study of compute precision of analog in-memory computing and demonstrated an accuracy of 92.81% on the CIFAR-10 image dataset. We believe this to be the highest level of accuracy of any currently reported chips using similar technology. In the paper, we also showed how we can seamlessly combine analog in-memory computing with several digital processing units and a digital communication fabric. The measured throughput per area for Giga-operations per second (GOPS) by area is a standard metric for describing compute efficiency where raw compute operations are normalized by a concomitant compute area. It essentially shows that there are more operations for a given area, meaning this chip is a more efficient compute engine. 8-bit input-output matrix multiplications of 400 GOPS/mm2 of the chip is more than 15 times higher than previous multi-core, in-memory computing chips based on resistive memory, while achieving comparable energy efficiency.

By combining the area- and energy-efficient analog-to-digital converters (ADCs), highly-linear multiply–accumulate-compute, and capable digital compute-blocks of this 64-tile chip with massively-parallel data-transport that we showed off in a 34-tile chip presented at the IEEE VLSI symposium in 2021, we now have demonstrated many of the building blocks needed to realize an architectural vision for a fast, low-power analog AI inference accelerator chip.

Using our learning we have designed an accelerator architecture like this which was published earlier this year in IEEE Transactions on VLSI systems . Our vision combines many analog in-memory computing tiles with a mix of special-purpose, digital compute-cores connected with a massively-parallel 2D mesh. In conjunction with sophisticated hardware-aware training we have developed in recent years, we expect these accelerators to deliver software-equivalent neural network accuracies across a wide variety of models in the years ahead.

- Abu Sebastian

- Manuel Le Gallo-Bourdeau

- Vijay Narayanan

- AI Hardware

- Semiconductors

- Note 1 : Phase-change memory (PCM) works when an electrical pulse is applied to a material, which changes the conductance of the device. The material switches between amorphous and crystalline phases, where a lower electrical pulse will make the device more crystalline, providing less resistance, and a higher electrical pulse makes the device more amorphous, resulting in more resistance. Instead of recording the usual 0s or 1s you would see in digital systems, the PCM device records its state as a continuum of values between the amorphous and crystalline states. This value is called a synaptic weight, which can be stored in the physical atomic configuration of each PCM. The memory is non-volatile, so the weights are retained when the power supply is switched off. ↩︎

- Note 2 : Giga-operations per second (GOPS) by area is a standard metric for describing compute efficiency where raw compute operations are normalized by a concomitant compute area. It essentially shows that there are more operations for a given area, meaning this chip is a more efficient compute engine. ↩︎

RRAM-based Analog In-Memory Computing : Invited Paper

Ieee account.

- Change Username/Password

- Update Address

Purchase Details

- Payment Options

- Order History

- View Purchased Documents

Profile Information

- Communications Preferences

- Profession and Education

- Technical Interests

- US & Canada: +1 800 678 4333

- Worldwide: +1 732 981 0060

- Contact & Support

- About IEEE Xplore

- Accessibility

- Terms of Use

- Nondiscrimination Policy

- Privacy & Opting Out of Cookies

A not-for-profit organization, IEEE is the world's largest technical professional organization dedicated to advancing technology for the benefit of humanity. © Copyright 2024 IEEE - All rights reserved. Use of this web site signifies your agreement to the terms and conditions.

News releases | Research | Science

April 30, 2024

Scientists solve chemical mystery at the interface of biology and technology

Researchers who want to bridge the divide between biology and technology spend a lot of time thinking about translating between the two different “languages” of those realms.

“Our digital technology operates through a series of electronic on-off switches that control the flow of current and voltage,” said Rajiv Giridharagopal , a research scientist at the University of Washington. “But our bodies operate on chemistry. In our brains, neurons propagate signals electrochemically, by moving ions — charged atoms or molecules — not electrons.”

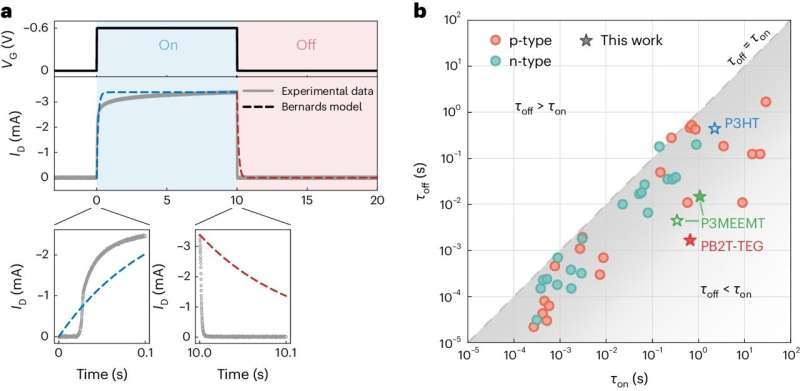

Implantable devices from pacemakers to glucose monitors rely on components that can speak both languages and bridge that gap. Among those components are OECTs — or organic electrochemical transistors — which allow current to flow in devices like implantable biosensors. But scientists long knew about a quirk of OECTs that no one could explain: When an OECT is switched on, there is a lag before current reaches the desired operational level. When switched off, there is no lag. Current drops almost immediately.

A UW-led study has solved this lagging mystery, and in the process paved the way to custom-tailored OECTs for a growing list of applications in biosensing, brain-inspired computation and beyond.

“How fast you can switch a transistor is important for almost any application,” said project leader David Ginger , a UW professor of chemistry, chief scientist at the UW Clean Energy Institute and faculty member in the UW Molecular Engineering and Sciences Institute. “Scientists have recognized the unusual switching behavior of OECTs, but we never knew its cause – until now.”

The six images shown here are microscope camera screen shots, showing the two-step turn-on process for an OECT. Figures on the left indicate time. When the OECT is first switched on, a dark front of ions propagates across the transistor from the side labeled “S” to the side labeled “D.” Afterward, the transistor continues to darken as additional charge-bearing particles move in. Nature Materials

In a paper published April 17 in Nature Materials, Ginger’s team at the UW — along with Professor Christine Luscombe at the Okinawa Institute of Science and Technology in Japan and Professor Chang-Zhi Li at Zhejiang University in China — report that OECTs turn on via a two-step process, which causes the lag. But they appear to turn off through a simpler one-step process.

In principle, OECTs operate like transistors in electronics: When switched on, they allow the flow of electrical current. When switched off, they block it. But OECTs operate by coupling the flow of ions with the flow of electrons, which makes them interesting routes for interfacing with chemistry and biology.

The new study illuminates the two steps OECTs go through when switched on. First, a wavefront of ions races across the transistor. Then, more charge-bearing particles invade the transistor’s flexible structure, causing it to swell slightly and bringing current up to operational levels. In contrast, the team discovered that deactivation is a one-step process: Levels of charged chemicals simply drop uniformly across the transistor, quickly interrupting the flow of current.

Knowing the lag’s cause should help scientists design new generations of OECTs for a wider set of applications.

“There’s always been this drive in technology development to make components faster, more reliable and more efficient,” Ginger said. “Yet, the ‘rules’ for how OECTs behave haven’t been well understood. A driving force in this work is to learn them and apply them to future research and development efforts.”

Whether they reside within devices to measure blood glucose or brain activity, OECTs are largely made up of flexible, organic semiconducting polymers — repeating units of complex, carbon-rich compounds — and operate immersed in liquids containing salts and other chemicals. For this project, the team studied OECTs that change color in response to electrical charge. The polymer materials were synthesized by Luscombe’s team at the Okinawa Institute of Science and Technology and Li’s at Zhejiang University, and then fabricated into transistors by UW doctoral students Jiajie Guo and Shinya “Emerson” Chen, who are co-lead authors on the paper.

“A challenge in the materials design for OECTs lies in creating a substance that facilitates effective ion transport and retains electronic conductivity,” said Luscombe, who is also a UW affiliate professor of chemistry and of materials science and engineering. “The ion transport requires a flexible material, whereas ensuring high electronic conductivity typically necessitates a more rigid structure, posing a dilemma in the development of such materials.”

The three images shown here are microscope camera screen shots, showing the one-step turn-off process for an OECT. Figures on the left indicate time. The OECT appears dark at the moment of switch-off because it is loaded with charge-bearing particles — also known as being fully “doped.” When the OECT is switched off, the number of charge-bearing particles drops rapidly across the transistor, lightening its color. Nature Materials

Guo and Chen observed under a microscope — and recorded with a smartphone camera — precisely what happens when the custom-built OECTs are switched on and off. It showed clearly that a two-step chemical process lies at the heart of the OECT activation lag.

Past research, including by Ginger’s group at the UW , demonstrated that polymer structure, especially its flexibility, is important to how OECTs function. These devices operate in fluid-filled environments containing chemical salts and other biological compounds, which are more bulky compared to the electronic underpinnings of our digital devices.

The new study goes further by more directly linking OECT structure and performance. The team found that the degree of activation lag should vary based on what material the OECT is made of, such as whether its polymers are more ordered or more randomly arranged, according to Giridharagopal. Future research could explore how to reduce or lengthen the lag times, which for OECTs in the current study were fractions of a second.

“Depending on the type of device you’re trying to build, you could tailor composition, fluid, salts, charge carriers and other parameters to suit your needs,” said Giridharagopal.

OECTs aren’t just used in biosensing. They are also used to study nerve impulses in muscles, as well as forms of computing to create artificial neural networks and understand how our brains store and retrieve information. These widely divergent applications necessitate building new generations of OECTs with specialized features, including ramp-up and ramp-down times, according to Ginger.

“Now that we’re learning the steps needed to realize those applications, development can really accelerate,” said Ginger.

Guo is now a postdoctoral researcher at the Lawrence Berkeley National Laboratory and Chen is now a scientist at Analog Devices. Other co-authors on the paper are Connor Bischak , a former UW postdoctoral researcher in chemistry who is now an assistant professor at the University of Utah; Jonathan Onorato, a UW doctoral alum and scientist at Exponent; and Kangrong Yan and Ziqui Shen of Zhejiang University. The research was funded by the U.S. National Science Foundation, and polymers developed at Zhejiang University were funded by the National Science Foundation of China.

For more information contact Ginger at [email protected] , Luscombe at [email protected] and Giridharagopal at [email protected] .

News releases

Read more news releases

Search UW News

Artificial intelligence, flooding and landslides, latest news releases.

7 hours ago

UW Today Newsletter

UW Today Daily

UW Today Week in Review

For UW employees

Be boundless, connect with us:.

© 2024 University of Washington | Seattle, WA

Suggestions or feedback?

MIT News | Massachusetts Institute of Technology

- Machine learning

- Social justice

- Black holes

- Classes and programs

Departments

- Aeronautics and Astronautics

- Brain and Cognitive Sciences

- Architecture

- Political Science

- Mechanical Engineering

Centers, Labs, & Programs

- Abdul Latif Jameel Poverty Action Lab (J-PAL)

- Picower Institute for Learning and Memory

- Lincoln Laboratory

- School of Architecture + Planning

- School of Engineering

- School of Humanities, Arts, and Social Sciences

- Sloan School of Management

- School of Science

- MIT Schwarzman College of Computing

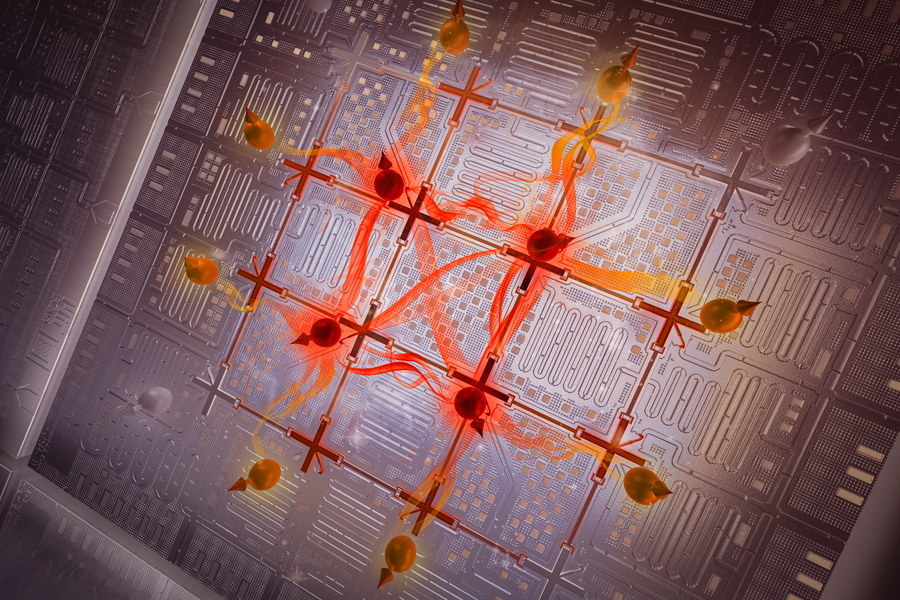

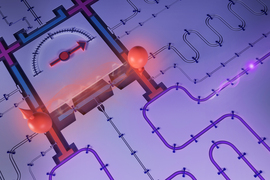

MIT scientists tune the entanglement structure in an array of qubits

Press contact :, media download.

*Terms of Use:

Images for download on the MIT News office website are made available to non-commercial entities, press and the general public under a Creative Commons Attribution Non-Commercial No Derivatives license . You may not alter the images provided, other than to crop them to size. A credit line must be used when reproducing images; if one is not provided below, credit the images to "MIT."

Previous image Next image

Entanglement is a form of correlation between quantum objects, such as particles at the atomic scale. This uniquely quantum phenomenon cannot be explained by the laws of classical physics, yet it is one of the properties that explains the macroscopic behavior of quantum systems.

Because entanglement is central to the way quantum systems work, understanding it better could give scientists a deeper sense of how information is stored and processed efficiently in such systems.