- Physical Design

- Assertion Based Verification

- Equivalence Checking

- Simulation Based

Slick on Silicon

Verilog: Continuous & Procedural Assignments

Continuous Assignment

Continuous assignment is used to drive a value on to a net in dataflow modeling. The net can be a vector or scalar, indexed part select, constant bit or part select of a vector. Concatenation is also supported with scalar vector types.

Regular & Implicit Assignment

Regular continuous assignment means, the declaration of a net and its continuous assignments are done in two different statements. But in implicit assignment, continuous assignment can be done on a net when it is declared itself. In the below example, `valid` is declared as wire during the assignment. If signal name is used to the left of the continuous assignment, an implicit net declaration will be inferred. In the below code `dout` is not declared as net, but it is inferred during assignment.

Procedural Assignment

We have already seen that continuous assignment updates net, but procedural assignment update values of reg, real, integer or time variable. The constant part select, indexed part select and bit select are possible for vector reg.

3 comments on “ Verilog: Continuous & Procedural Assignments ”

Excellent blog

Clearly explained.. Thanks

sir what’s your company/industry name.

Leave a Reply Cancel reply

Your email address will not be published. Required fields are marked *

Save my name, email, and website in this browser for the next time I comment.

Procedural continuous assignments

Till now we have seen two types of assignments i.e. continuous assignment and procedural assignment .

The continuous assignment is used to drive net data type variables using the ‘assign’ statements whereas procedural assignments are used to drive reg data type variables using initial and always block statements.

Verilog also provides a third type of assignment i.e. procedural continuous assignment that drives net or reg data type variables for a certain period of time by overriding the existing assignments.

There are two types of procedural continuous assignments

assign and deassign

Force and release.

The assign and deassign statements control reg type variable values by overriding existing procedural assignments for a limited time period. After the execution of the deassign statement, another procedural or procedural continuous assignment can change the variable value once again, till then the previous value can hold.

The d1 = 3 is assigned at #5 time units and deassign at #10 time units.The d1 = 3 retains till next assignment d1 = 7 happens at 20 time units.

The force and release statements control net and reg data type variable values by overriding existing procedural, continuous or procedural continuous assignments for a limited time period. After the execution of the release statement for the reg data type variable, another procedural or procedural continuous assignment can change the variable value once again, till then the previous value can hold. The value of the previous continuous assignment retains in the case of the net data type variable.

The d1 belongs to the reg data type and d2 belongs to the net data type. Both variables are forced at #5 time units and released at #10 time units Once, it is released,

- The d1 value remains the same (d1 = 3) until it is changed to d1 = 7 at 20 time units.

- The d2 value holds a previously assigned value using continuous assignment (d2 = 2).

Verilog Tutorials

Verilog Assignments

Variable declaration assignment, net declaration assignment, assign deassign, force release.

- Procedural continuous

Legal LHS values

An assignment has two parts - right-hand side (RHS) and left-hand side (LHS) with an equal symbol (=) or a less than-equal symbol (<=) in between.

The RHS can contain any expression that evaluates to a final value while the LHS indicates a net or a variable to which the value in RHS is being assigned.

Procedural Assignment

Procedural assignments occur within procedures such as always , initial , task and functions and are used to place values onto variables. The variable will hold the value until the next assignment to the same variable.

The value will be placed onto the variable when the simulation executes this statement at some point during simulation time. This can be controlled and modified the way we want by the use of control flow statements such as if-else-if , case statement and looping mechanisms.

An initial value can be placed onto a variable at the time of its declaration as shown next. The assignment does not have a duration and holds the value until the next assignment to the same variable happens. Note that variable declaration assignments to an array are not allowed.

If the variable is initialized during declaration and at time 0 in an initial block as shown below, the order of evaluation is not guaranteed, and hence can have either 8'h05 or 8'hee.

Procedural blocks and assignments will be covered in more detail in a later section.

Continuous Assignment

This is used to assign values onto scalar and vector nets and happens whenever there is a change in the RHS. It provides a way to model combinational logic without specifying an interconnection of gates and makes it easier to drive the net with logical expressions.

Whenever b or c changes its value, then the whole expression in RHS will be evaluated and a will be updated with the new value.

This allows us to place a continuous assignment on the same statement that declares the net. Note that because a net can be declared only once, only one declaration assignment is possible for a net.

Procedural Continuous Assignment

- assign ... deassign

- force ... release

This will override all procedural assignments to a variable and is deactivated by using the same signal with deassign . The value of the variable will remain same until the variable gets a new value through a procedural or procedural continuous assignment. The LHS of an assign statement cannot be a bit-select, part-select or an array reference but can be a variable or a concatenation of variables.

These are similar to the assign - deassign statements but can also be applied to nets and variables. The LHS can be a bit-select of a net, part-select of a net, variable or a net but cannot be the reference to an array and bit/part select of a variable. The force statment will override all other assignments made to the variable until it is released using the release keyword.

- The Verilog-AMS Language

- Continuous Assigns

Continuous Assigns

A module may have any number of continuous assign statements. Continuous assign statements are used to drive values on to wires. For example:

This is referred to as a continuous assign because the wire on the left-hand side of the assignment operator is continuously driven with the value of the expression on the right hand side. The target of the assign statement must be a wire. The continuous assign statement is not a procedural statement and so must be used at the module level; it cannot be placed in an initial or always process.

You can add delay to a continuous assign statement as follows:

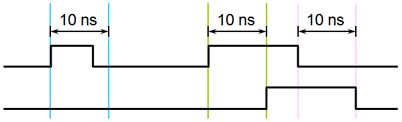

In this case, the value of a changes 10 units of time after the expression b & c changes. Continuous assign statement implement inertial delay, meaning that continuous assign statements swallow glitches. This is illustrated below with the assumption that the unit of time is 1ns.

It is possible to specify up to three delay values on a continuous assignment:

When you specify more than one:

The first delay refers to the transition to the 1 value (rise delay).

The second delay refers to the transition to the 0 value (fall delay).

The third delay refers to the transition to the high-impedance value.

When a value changes to the unknown (x) value, the delay is the smallest of the delays specified.

If only two delays are specified, then the delay to high-impedance is the smallest of the two values specified.

A continuous assignment drives a value into a net.

Description:

Continuous assignments model combinational logic. Each time the expression changes on the right-hand side, the right-hand side is re-evaluated, and the result is assigned to the net on the left-hand side.

The implicit continuous assignment combines the net declaration (see Net data type) and continuous assignment into one statement. The explicit assignment require two statements: one to declare the net (see Net data type), and one to continuously assign a value to it.

Continuous assignments are not the same as procedural continuous assignments. Continuous assignments are declared outside of procedural blocks. They automatically become active at time zero, and are evaluated concurrently with procedural blocks, module instances, and primitive instances.

Net data type , Procedural continuous assignment

Procedural and Continuous Assignments

- First Online: 07 July 2021

Cite this chapter

- Ashok B. Mehta 2

2443 Accesses

This chapter will delve into the nuances of procedural and continuous assignments. It discusses features such as blocking and non-blocking procedural assignment, assign/deassign, force-release, etc.

Electronic Supplementary Material The online version of this chapter ( https://doi.org/10.1007/978-3-030-71319-5_23 ) contains supplementary material, which is available to authorized users.

This is a preview of subscription content, log in via an institution to check access.

Access this chapter

- Available as PDF

- Read on any device

- Instant download

- Own it forever

- Available as EPUB and PDF

- Compact, lightweight edition

- Dispatched in 3 to 5 business days

- Free shipping worldwide - see info

- Durable hardcover edition

Tax calculation will be finalised at checkout

Purchases are for personal use only

Institutional subscriptions

Author information

Authors and affiliations.

DefineView Consulting, Los Gatos, CA, USA

Ashok B. Mehta

You can also search for this author in PubMed Google Scholar

Rights and permissions

Reprints and permissions

Copyright information

© 2021 The Author(s), under exclusive license to Springer Nature Switzerland AG

About this chapter

Mehta, A.B. (2021). Procedural and Continuous Assignments. In: Introduction to SystemVerilog. Springer, Cham. https://doi.org/10.1007/978-3-030-71319-5_23

Download citation

DOI : https://doi.org/10.1007/978-3-030-71319-5_23

Published : 07 July 2021

Publisher Name : Springer, Cham

Print ISBN : 978-3-030-71318-8

Online ISBN : 978-3-030-71319-5

eBook Packages : Engineering Engineering (R0)

Share this chapter

Anyone you share the following link with will be able to read this content:

Sorry, a shareable link is not currently available for this article.

Provided by the Springer Nature SharedIt content-sharing initiative

- Publish with us

Policies and ethics

- Find a journal

- Track your research

Very Large Scale Integration (VLSI)

VLSI Encyclopedia - Connecting VLSI Engineers

Featured post

Top 5 books to refer for a vhdl beginner.

VHDL (VHSIC-HDL, Very High-Speed Integrated Circuit Hardware Description Language) is a hardware description language used in electronic des...

Sunday 9 September 2012

Procedural continuous assignments.

assign register_assignment ; deassign register_left_value ; force register_assignment | net_assignment ; release register_left_value | net_left_value ; register_left_value - left hand-side operand ; net_left_value - left hand-side operand ;

module example1(clk, d, reset, set, q) ; input clk, d, reset, set; output q; reg q; always @ ( posedge clk) q = d; always @ (reset or set) begin if (reset) assign q = 1'b0; else if (set) assign q= 1'b1; else deassign q; end endmodule

- Assign and deassign can only be applied to reg type variables.

No comments:

Post a comment.

Please provide valuable comments and suggestions for our motivation. Feel free to write down any query if you have regarding this post.

- Understanding real, realtime and shortreal variables of SystemVerilog This post will help you to understand the difference between real, realtime and shortreal data types of SystemVerilog and its usage. ...

- SystemVerilog Constants In previous post of this SystemVerilog Tutorial we talked about enumerated type in detail. Now we will look at the constants in SystemVe...

IMAGES

VIDEO

COMMENTS

IEEE Std 1800-2012 C.4.2 Procedural assign and deassign statements: The procedural assign and deassign statements can be a source of design errors and can be an impediment to tool implementation. The procedural assign and deassign statements do not provide a capability that cannot be done by another method that avoids these problems. Therefore ...

1. There will be a few more issues in your code. 1. assign l1 = a & b; assign l2 = a | b; The primary rule with continuous assignments is that the LHS must be a net. The reason for this rule is that registers get values at discrete times, but nets are always driven by a value. Changes to a net may happen asynchronously.

assign A = B; versus. alway_comb A = B; In this example, like many other constructs in Verilog, there is overlapping functionality. One of the biggest differences is that only the assign statement can be used to make an assignment to a net/wire. In SystemVerilog, you can use either statement to make assignments to a variable.

Continuous Assignment. Continuous assignment is used to drive a value on to a net in dataflow modeling. The net can be a vector or scalar, indexed part select, constant bit or part select of a vector. Concatenation is also supported with scalar vector types. module Conti_Assignment (addr1,addr2,wr,din,valid1,valid2,dout); input [31:0] addr1,addr2;

Procedural continuous assignments. Till now we have seen two types of assignments i.e. continuous assignment and procedural assignment. The continuous assignment is used to drive net data type variables using the 'assign' statements whereas procedural assignments are used to drive reg data type variables using initial and always block ...

You cannot assign a value to a reg through continuous assignment. A wire (net) type variable can be used to connect signals together using continuous assignment. This is either the assign statement or by being ... you declared your outputs as reg inside the module, this is fine because they are being driven from procedural blocks in the module ...

Description: Procedural assignments are used for updating register data types and memory data types. The expression in a blocking procedural assignment is evaluated and assigned when the statement is encountered. In a begin-end sequential statement group, execution of the next statement is blocked until the assignment is complete. In a non ...

The value of the variable will remain same until the variable gets a new value through a procedural or procedural continuous assignment. The LHS of an assign statement cannot be a bit-select, part-select or an array reference but can be a variable or a concatenation of variables. reg q; initial begin assign q = 0; #10 deassign q; end force ...

If some branches in the process are not explicitly assigning some net, it is implicitly assigned with the previous value with an inferred latch. So there is no situation the process won't drive this signal (unless explicitly assigning hi-Z to it..). Update:

Procedural continuous assignments are typically used for timed intervals. A simple example is shown below by using assign and deassign statements. reg q; initial begin. assign q = 0; #20 deassign q; end. We overrode the assignment on q in the preceding example and applied new values to it.

nets. Continuous assignments, as the name suggests, drive the net/variable continu-ously. As soon as the right-hand side (RHS) of the assignment changes, the left- hand side (LHS) of the assignment will change. Think of RHS as a combinational circuit that drives the net continuously. Procedural assignments assign values to variables.

Instead of the continuous assignment statement, the net declaration assignment can be used. This means that in the net declaration statement we can assign expressions that occur whenever right-hand side operands change. In this case, assign keyword is not used. Example 1 can be described as shown in Example 4. In this case a net can be declared ...

The explicit assignment require two statements: one to declare the net (see Net data type), and one to continuously assign a value to it. Continuous assignments are not the same as procedural ...

Continuous assign statements are used to drive values on to wires. For example: assign a = b & c; This is referred to as a continuous assign because the wire on the left-hand side of the assignment operator is continuously driven with the value of the expression on the right hand side. The target of the assign statement must be a wire.

Description. In the assign statement, the left hand-side operand can be a register or a concatenation of registers in contrast to continuous assignments where the left hand-side operands are nets. However, the memory word, bit-select or part-select cannot be used on the left hand-side. The priority of procedural continuous assignment is higher ...

The key part is: reg cannot be driven by ... continuous assignment.. Variables declared as type reg can only be assigned in procedural blocks, they cannot be connected to our ports of a submodule.. For example you have output reg temp and try to drive it from the output port of submodule PIPO:p1.temp.Instead you should have output temp in your data_path module (the same for Product).

The explicit assignment require two statements: one to declare the net (see Net data type), and one to continuously assign a value to it. Continuous assignments are not the same as procedural continuous assignments. Continuous assignments are declared outside of procedural blocks. They automatically become active at time zero, and are evaluated ...

There are two continuous assignments in the model. "assign a = b;" will change the value of "a" whenever the value of "b" changes. Value of "a" can change from a procedural assignment or from another continuous assignment. Similarly, "assign bus = c + b;" causes "bus" to change whenever the expression "c + b" changes.

Description. In the assign statement, the left hand-side operand can be a register or a concatenation of registers in contrast to continuous assignments where the left hand-side operands are nets. However, the memory word, bit-select or part-select cannot be used on the left hand-side. The priority of procedural continuous assignment is higher ...

Formal Definition. Procedural continuous assignments provide a means to continuously drive a value into a register or a net. Simplified Syntax. Description. In the assign statement, the left hand-side operand can be a register or a concatenation of registers in contrast to continuous assignments where the left hand-side operands are nets.