How to use a procedure in a process in VHDL

It is possible to drive external signals from a procedure. As long as the signal is within the scope of the procedure, it can be accessed for reading or writing, even if it isn’t listed in the parameter list.

Procedures that are declared in the declarative region of the architecture, cannot drive any external signals. This is simply because there are no signals in its scope at compile time. A procedure declared within a process, on the other hand, will have access to all of the signals that the process can see.

This blog post is part of the Basic VHDL Tutorials series.

Such procedures can be used for decluttering algorithms in processes where the same operations occur several times. We could use a normal procedure where all the inputs and outputs are assigned to local signals when you call it, but that is not the point. By omitting the input and output signals from the procedure call, we must type less, and more importantly, we make the code more readable.

Imagine a process implementing a complex communication protocol. It would be a lot easier to understand the execution flow of the main algorithm if some operations were replaced by procedure calls like RequestToSend() or SendAutorizationHeader() . You would know what those lines did just be looking at the procedure names.

In the previous tutorial , we simplified our finite-state machine (FSM) code by using an impure function. We were driving the Counter signal from the impure function, and we used the return value to determine when to change state. But what if we want to move the assignment of the State signal into the function as well, and ignore the return value?

It’s not possible to call a function without assigning the return value to something in VHDL. If we try to do so, ModelSim will produce the compile error: No feasible entries for subprogram “CounterExpired” .

Instead, we can use a procedure for this. A procedure declared within a process can access any signal within the scope of that process. This is similar to the impure function, but since it’s a procedure, there is no return value.

In this video tutorial we will simplify the FSM code by using a procedure declared in a process:

The final code for the Procedure in Process testbench :

The final code for the Traffic Lights module :

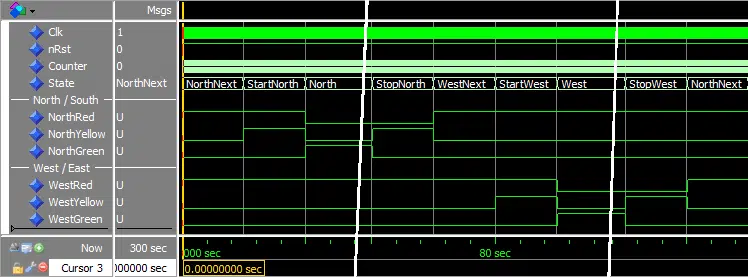

The waveform after we entered the run 5 min command in the ModelSim console:

Let me send you a Zip with everything you need to get started in 30 seconds

Unsubscribe at any time

We haven’t changed the behavior of the module, and we can see that the waveform is unchanged.

Compared to the code from the tutorial where we initially created the traffic lights module , the FSM code is much more readable now. You can easily follow the algorithm that it implements by reading the code. Having the timer and state change logic in a single procedure is beneficial because it ensures that it’s implemented equally everywhere it’s used.

- A procedure declared in a process can access any signal within the scope of that process

- Procedures within processes can be used for improving code readability

I’m from Norway, but I live in Bangkok, Thailand. Before I started VHDLwhiz, I worked as an FPGA engineer in the defense industry. I earned my master’s degree in informatics at the University of Oslo.

Similar Posts

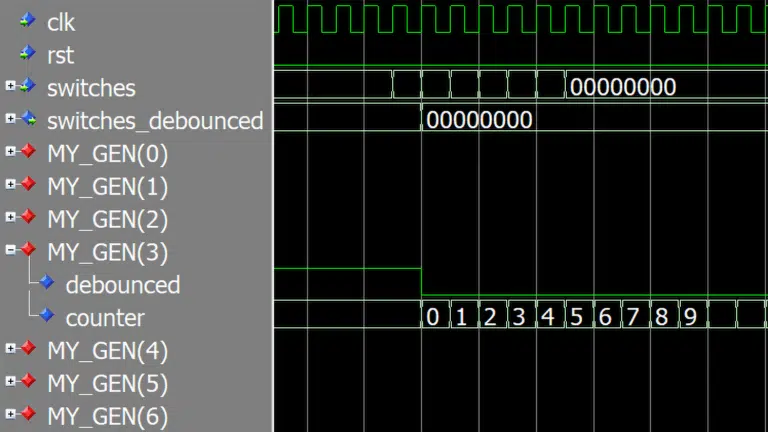

Generate statement debouncer example

The generate statement in VHDL can automatically duplicate a block of code to closures with identical signals, processes, and instances. It’s a for loop for the architecture region that can create chained processes or module instances.

How to create a timer in VHDL

In earlier tutorials we have used the wait for statement to delay time in simulation. But what about production modules? The wait for statement cannot be used for that. That only works in simulation because we can’t just tell the electrons in a circuit to pause for a given time. So how can we keep…

How to use Signed and Unsigned in VHDL

The signed and unsigned types in VHDL are bit vectors, just like the std_logic_vector type. The difference is that while the std_logic_vector is great for implementing data buses, it’s useless for performing arithmetic operations. If you try to add any number to a std_logic_vector type, ModelSim will produce the compilation error: No feasible entries for…

Why you always need a testbench

As most hardware engineers, I started off my computer science career by learning a sequential programming language. The first language I learned at the University of Oslo was Java. While it’s not considered to be the most exciting language today, at the time, Java was at the pinnacle of its popularity. The engineers who built…

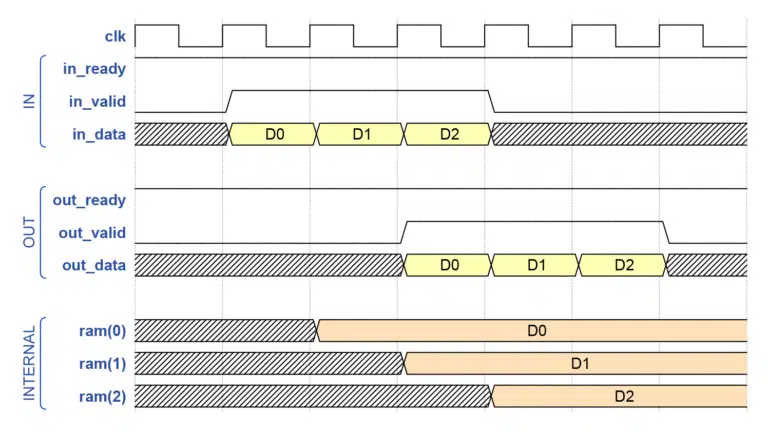

How to make an AXI FIFO in block RAM using the ready/valid handshake

I was a little annoyed by the peculiarities of the AXI interface the first time I had to create logic to interface an AXI module. Instead of the regular busy/valid, full/valid, or empty/valid control signals, the AXI interface uses two control signals named “ready” and “valid”. My frustration soon changed to awe. The AXI interface…

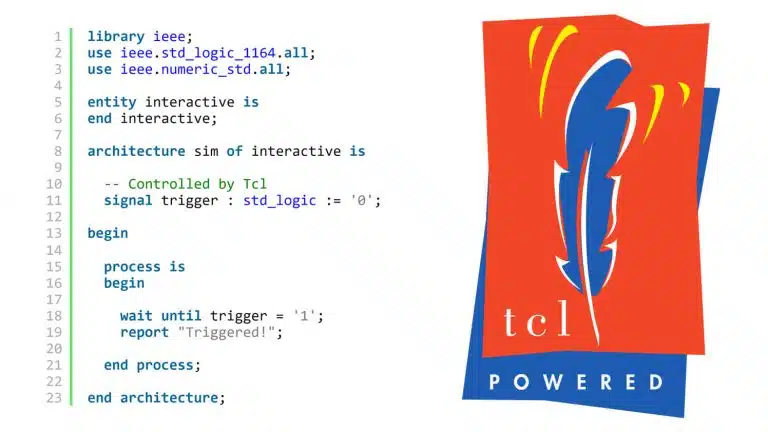

Interactive testbench using Tcl

An interactive testbench is a simulator setup where input to the device under test (DUT) is provided by an operator while the testbench is running. Most often, this would mean you entering commands in the simulator console to provide the DUT with stimulus. While you should always create a self-checking testbench, an interactive testbench can…

Thank you for this blog post! While writing procedure why did you not indicate “in”- “out”s and “signals”-“constant”s, like you did in the procedure video? Is it about “procedure” being in “progress”?

That’s a good observation and a great question!

Let’s see what the VHDL standard has to say: “If no object class is explicitly given, constant is assumed.”

And a constant always has “in” mode. Therefore, our parameter list is implicitly the same as this:

Great lesson as always. Just a contribution: I think there is a error in the text where you say “This is similar to the impure process”, you actually mean “impure function”, right?

Thanks, Rafael. You are entirely correct. I’ve changed the erroneous text to “impure function”. ?

Leave a Reply Cancel reply

Your email address will not be published. Required fields are marked *

Notify me of replies to my comment via email

Procedure Statement – VHDL Example

Procedures are part of a group of structures called subprograms. Procedures are small sections of code that perform an operation that is reused throughout your code. This serves to cleanup code as well as allow for reusability.

Procedures can take inputs and generate outputs. They can generally be more complicated than functions . It is not required to pass any signals to a procedure. In the example below there is a procedure p_INCREMENT_SLV whose purpose is to increment a standard logic vector by 1 and generate a signal with the result.

One additional note about using wait statements: Wait statements CAN be used in a procedure, as long as the process that calls the procedure does not have a sensitivity list. In the example below the procedure has a 1 ns wait statement to demonstrate this. This makes procedures useful for creating testbench code.

Learn Verilog

Leave A Comment Cancel reply

Save my name, email, and website in this browser for the next time I comment.

- Product Manual

- Release Notes

- Screencasts

- Tech Articles

Signal Assignments in VHDL: with/select, when/else and case

Sometimes, there is more than one way to do something in VHDL. OK, most of the time , you can do things in many ways in VHDL. Let’s look at the situation where you want to assign different values to a signal, based on the value of another signal.

With / Select

The most specific way to do this is with as selected signal assignment. Based on several possible values of a , you assign a value to b . No redundancy in the code here. The official name for this VHDL with/select assignment is the selected signal assignment .

When / Else Assignment

The construct of a conditional signal assignment is a little more general. For each option, you have to give a condition. This means that you could write any boolean expression as a condition, which give you more freedom than equality checking. While this construct would give you more freedom, there is a bit more redundancy too. We had to write the equality check ( a = ) on every line. If you use a signal with a long name, this will make your code bulkier. Also, the separator that’s used in the selected signal assignment was a comma. In the conditional signal assignment, you need the else keyword. More code for the same functionality. Official name for this VHDL when/else assignment is the conditional signal assignment

Combinational Process with Case Statement

The most generally usable construct is a process. Inside this process, you can write a case statement, or a cascade of if statements. There is even more redundancy here. You the skeleton code for a process (begin, end) and the sensitivity list. That’s not a big effort, but while I was drafting this, I had put b in the sensitivity list instead of a . Easy to make a small misstake. You also need to specify what happens in the other cases. Of course, you could do the same thing with a bunch of IF-statements, either consecutive or nested, but a case statement looks so much nicer.

While this last code snippet is the largest and perhaps most error-prone, it is probably also the most common. It uses two familiar and often-used constructs: the process and the case statements.

Hard to remember

The problem with the selected and conditional signal assignments is that there is no logic in their syntax. The meaning is almost identical, but the syntax is just different enough to throw you off. I know many engineers who permanenty have a copy of the Doulos Golden Reference Guide to VHDL lying on their desks. Which is good for Doulos, because their name gets mentioned all the time. But most people just memorize one way of getting the job done and stick with it.

- VHDL Pragmas (blog post)

- Records in VHDL: Initialization and Constraining unconstrained fields (blog post)

- Finite State Machine (FSM) encoding in VHDL: binary, one-hot, and others (blog post)

- "Use" and "Library" in VHDL (blog post)

- The scope of VHDL use clauses and VHDL library clauses (blog post)

In VHDL -93, any signal assignment statement may have an optional label:

IMAGES

VIDEO

COMMENTS

Any variable which does not assign its value to a signal, but only to other variables, is a perfectly acceptable "wire". My understanding of the whole subject is this: A signal assignment inside a process will disregard other signal assignments made in the same process "instantiation".

A procedure doesn’t return a value like a function does, but you can return values by declaring out or inout signals in the parameter list. This blog post is part of the Basic VHDL Tutorials series. The basic syntax for creating a procedure is: procedure <procedure_name>. (signal|variable|constant <name1> : in|out|inout <type>;

A procedure declared within a process can access any signal within the scope of that process. This is similar to the impure function, but since it’s a procedure, there is no return value. In this video tutorial we will simplify the FSM code by using a procedure declared in a process: The final code for the Procedure in Process testbench: 1.

Procedure Statement – VHDL Example. Procedures are part of a group of structures called subprograms. Procedures are small sections of code that perform an operation that is reused throughout your code. This serves to cleanup code as well as allow for reusability. Procedures can take inputs and generate outputs.

sequential statements. Procedures may have in, out or inout parameters. These may be signal, variable or constant. the default for in parameters is constant. For out and inout it is variable. In fact, a constant in parameter can be associated with a signal, variable constant or expression when the procedure is called: (ALARM_TIME, CURRENT_TIME ...

1. The Inside_process and Outside_process versions behave differently. If both designs work, it is mostly out of luck, because in this case Out_signal simply lags half a clock cycle when declared inside the process. Out_signal is assigned when the process triggers, which in this case occurs on rising and falling edges of clk.

A bus is a collection of wires related in some way by function or clock domain. Examples would be an address bus or data bus. In VHDL we refer to busses as a vector. For example: --8-bit bus consisting of 8 wires carrying signals of -- type std_logic --all these wires may be referred to by the name big_bus. SIGNAL big_bus : STD_LOGIC_VECTOR(7 ...

Section 3 - Signals and Processes. This section is short, but contains important information about the use of signals in the process statement. The issue of concern is to avoid confusion about the difference between how a signal assignment and variable assignment behave in the process statement. Remember a signal assignment, if anything, merely ...

With / Select. The most specific way to do this is with as selected signal assignment. Based on several possible values of a, you assign a value to b. No redundancy in the code here. The official name for this VHDL with/select assignment is the selected signal assignment. with a select b <= "1000" when "00", "0100" when "01", "0010" when "10 ...

The rules about what happpens when a delayed signal assignment is subsequently overridden are complex: see the LRM section 8.3.1 or "A VHDL Primer" by Jayaram Bhasker, section 4.14: A delayed sequential signal assignment does not suspend the process or procedure for the time specified.