FPGA Architecture: Principles and Progression

Ieee account.

- Change Username/Password

- Update Address

Purchase Details

- Payment Options

- Order History

- View Purchased Documents

Profile Information

- Communications Preferences

- Profession and Education

- Technical Interests

- US & Canada: +1 800 678 4333

- Worldwide: +1 732 981 0060

- Contact & Support

- About IEEE Xplore

- Accessibility

- Terms of Use

- Nondiscrimination Policy

- Privacy & Opting Out of Cookies

A not-for-profit organization, IEEE is the world's largest technical professional organization dedicated to advancing technology for the benefit of humanity. © Copyright 2024 IEEE - All rights reserved. Use of this web site signifies your agreement to the terms and conditions.

- IEEE Xplore Digital Library

- IEEE Standards

- IEEE Spectrum

IEEE Future Directions

Current trends and future directions in security of fpga applications with focus on thin clients.

Cameron Collins, University of Wisconsin – Green Bay and Ankur Chattopadhyay, Northern Kentucky University

1. Introduction

Recent high-profile security flaws in conventional desktop and server processors have brought increased interest and attention to the risks posed by proprietary hardware and the closely guarded, obfuscated firmware that tends to accompany it. 1 Adoption of open-source hardware and firmware could potentially address this issue. However, bringing any hardware based intellectual property (IP) to production through traditional methods may affect people plus organizations and may involve legal implications within the product’s supply chain. 2 Additionally, a large attack surface poses a problem. Field-programmable gate arrays (FPGAs) can prospectively address this concern, as they can be programmed and functionally verified directly by organizations which use them.

It can be argued that performance constraints, like speed, make FPGA-based systems a questionable substitute for the fast, integrated processors and system-on-chips used in traditional endpoint devices, but functionalities related to the core FPGA IP can be implemented in a GUI based thin client. Hence, a GUI based thin client, which can simulate the core FPGA functional logic, can be utilized as a safer i.e., a less risky, option to use with current systems, because it has lesser strings attached, as it does not involve hardware or a sizeable attack surface, and helps counter the FPGA overhead. This article seeks to explore current FPGA-ready applications and discusses future directions and potential opportunities, where FPGA can be securely implemented, i.e., simulated via a SPICE thin client, which is a modern remote desktop protocol. 3 To begin with, we next discuss some security components associated with FPGA.

Cryptography, video operations and networking are security related elements that form sound use cases for FPGAs. They benefit from the isolation and platform assurance that FPGAs offer. As a means of ensuring confidentiality and integrity of the communications between client and server, cryptographic processing applied in FPGA applications offers additional protection. Next, rendering and video decoding not only constitute a major part of a thin client’s computational workload, but are also security-critical functions. A compromised video decoding in a display system could be used to capture sensitive information from the screen or trick the users into actions that would benefit the attacker. Lastly, networking components are important to security as well. The networking stack is the first attack surface that a remote adversary will encounter during an attempted intrusion. It is also the last and only barrier to deal with in the path to data exfiltration.

2. The SPICE Protocol Features

As a newer offering, the SPICE protocol contains several convenient features that enable its usage in a modern enterprise setting. For example, the reference server implementation is designed for use with solutions, such as QEMU, 3 allowing it to be easily integrated into a desktop virtualization stack. It also supports multiple displays along with USB, audio, and smartcard redirection. It can heuristically identify areas of the screen on which videos are being displayed and apply bandwidth-efficient lossy compression to them, thereby reducing the load upon networking resources required to preserve a given framerate during multimedia consumption.

Finally, SPICE is an open source, commercially backed, and actively maintained project. However, some of its design goals may complicate attempts to build a thin client that relies on FPGAs. For instance, its creators have sought to offload most of the intensive CPU and GPU tasks to the client. To this end, the client is charged with reconstructing the complete screen from images that may be transmitted in a variety of ways via 2D vector graphics primitives. 4 This helps avoid the need of more powerful FPGA hardware and more complex graphics IP cores for speedy rendering in a thin client where SPICE is used.

3. Benefits of FPGA in a SPICE Thin Client

Several functions in SPICE can be relocated to special-purpose coprocessors implemented on FPGAs. Such an approach has a variety of potential benefits. For instance, it would help isolate security-critical functions from each other as well as any buggy, vulnerable, or untrusted software that might be running on the general-purpose processor. It may also help reduce the impact that semiconductor product lifecycles may have on the thin client’s service lifespan. The use of FPGA-compatible soft cores to replace out-of-production semiconductor components has already been studied. 5 It may be easier for large-volume customers to negotiate for extended production of one FPGA than several discrete components. When the chosen FPGA is no longer manufactured, a pin-compatible successor may well be available. If an IP core contains fundamental security flaws, then it can be replaced through enough resources by a comparable alternative without requiring changes to physical hardware. The configuration of a device’s FPGA(s) could be updated in the field, if a secure mechanism for doing so is provided.

4. SPICE FPGA: Security Angles and Future Work

FPGA-ready hardware implementations of cryptosystems, including AES 6, 7, 8 and RSA 9, 10 are used to authenticate the client with the server in SPICE. x22519, as used in elliptic curve Diffie-Hellman key exchanges, have been also used in this regard by researchers. 11 AES can be used as part of the networking stack in a Wi-Fi capable thin client. RSA and x22519 can be employed by Transport Layer Services (TLS), which is supported by the SPICE server for securing communication channels. 9, 11

SPICE can use multiple methods to send video from server to client. The server transmits areas of the display determined to contain video as MJPEG streams to save bandwidth. 12 Several FPGA-based JPEG decoders have been demonstrated by researchers. 13 Even early designs proved capable of processing 30 frames per second on then-current hardware. As MJPEG streams consist simply of a sequence of separately encoded JPEG images, these JPEG decoders might be good candidates for adaption to MJPEG. Other parts of the screen may be sent as images compressed by one of the following lossless algorithms, namely QUIC, which is a “global” extension of LZ and is specific to SPICE, or LZSS. 14 Researchers have successfully implemented a decompressor for DEFLATE, 15 which incorporates LZSS on an FPGA, and can be supported.

Image decoding or decompression on FPGAs has been explored, and SPICE allows parts of the frame to be reproduced by 2D vector graphics commands. For instance, text and primitive shapes can be rendered directly on the client rather than being transmitted as an image. In this context, a SPICE client may be served by Cairo, a sizable graphics library. Vector graphics rasterizers have been created for FPGAs, 4 but whether their capabilities meet the requirements of the SPICE protocol remains an open research question.

5. Summary

Overall, the SPICE protocol, as discussed in this article, can be potentially used as a thin client with FPGA applications, i.e., as a SPICE FPGA for an overall more optimal, secure and practical implementation. However, as discussed and pointed out in this article, there are a few specific aspects of this usage of a thin client with FPGAs that need to be explored in detail as part of future research. Also, another scope of future work is to compare the performance of SPICE with that of other available thin clients, which can be used with FPGA applications.

References

- V. Narayanan, M. S. Baranowski, L. Ryzhyk, Z. Rakamarić, and A. Burtsev, “RedLeaf: Towards An Operating System for Safe and Verified Firmware,” HotOS 2019 , 2019.

- S. Ray, E. Peeters, M. M. Tehranipoor and S. Bhunia, “System-on-Chip Platform Security Assurance: Architecture and Validation,” in Proceedings of the IEEE , vol. 106, no. 1, pp. 21-37, Jan. 2018. doi: 10.1109/JPROC.2017.2714641.

- “ Home ,” SPICE . [Online] [Accessed: 10-Nov-2019].

- S. G. Ramanathan, B. P. Kumar, C. M. Ananda and E. P. Jayakumar, “Design of graphics processing framework on FPGA,” 2016 IEEE International Conference on Recent Trends in Electronics, Information & Communication Technology (RTEICT) , Bangalore, 2016, pp. 387-391. doi: 10.1109/RTEICT.2016.7807847.

- Z. Zhang, L. Njilla, C. Kamhoua, K. Kwiat and Q. Yu, “Securing FPGA-based obsolete component replacement for legacy systems,” 2018 19th International Symposium on Quality Electronic Design (ISQED) , Santa Clara, CA, 2018, pp. 401-406. doi: 10.1109/ISQED.2018.8357320.

- M. Rao, A. Kaknjo, E. Omerdic, D. Toal and T. Newe, “An Efficient High Speed AES Implementation Using Traditional FPGA and LabVIEW FPGA Platforms,” 2018 International Conference on Cyber-Enabled Distributed Computing and Knowledge Discovery (CyberC) , Zhengzhou, China, 2018, pp. 93-937. doi: 10.1109/CyberC.2018.00028.

- N. Gaur, A. Mehra and P. Kumar, “Enhanced AES Architecture using Extended Set ALU at 28nm FPGA,” 2018 5th International Conference on Signal Processing and Integrated Networks (SPIN) , Noida, 2018, pp. 437-440. doi: 10.1109/SPIN.2018.8474090.

- S. U. Jonwal and P. P. Shingare, “Advanced Encryption Standard (AES) implementation on FPGA with hardware in loop,” 2017 International Conference on Trends in Electronics and Informatics (ICEI) , Tirunelveli, 2017, pp. 64-67, doi: 10.1109/ICOEI.2017.8300776.

- T. Isobe, S. Tsutsumi, K. Seto, K. Aoshima and K. Kariya, “10 Gbps implementation of TLS/SSL accelerator on FPGA,” 2010 IEEE 18th International Workshop on Quality of Service (IWQoS) , Beijing, 2010, pp. 1-6. doi: 10.1109/IWQoS.2010.5542723.

- A. Thiruneelakandan and T. Thirumurugan, “An approach towards improved cyber security by hardware acceleration of OpenSSL cryptographic functions,” 2011 International Conference on Electronics, Communication and Computing Technologies , Pauls Nagar, 2011, pp. 13-16. doi:10.1109/ICECCT.2011.6077061.

- P. Sasdrich and T. Géneysu, “Cryptography for next generation TLS: Implementing the RFC 7748 elliptic Curve 448 cryptosystem in hardware,” 2017 54th ACM/EDAC/IEEE Design Automation Conference (DAC) , Austin, TX, 2017, pp. 1-6. doi: 10.1145/3061639.3062222.

- L. Chen, N. Shashidhar and Q. Liu, “Scalable Secure MJPEG Video Streaming,” 2012 26th International Conference on Advanced Information Networking and Applications Workshops , Fukuoka, 2012, pp. 111-115. doi: 10.1109/WAINA.2012.163.

- G. Kyrtsakas and R. Muscedere, “An FPGA implementation of a custom JPEG image decoder SoC module,” 2017 IEEE 30th Canadian Conference on Electrical and Computer Engineering (CCECE) , Windsor, ON, 2017, pp. 1-4. doi: 10.1109/CCECE.2017.7946826.

- I. Shcherbakov, C. Weis and N. Wehn, “A High-Performance FPGA-Based Implementation of the LZSS Compression Algorithm,” 2012 IEEE 26th International Parallel and Distributed Processing Symposium Workshops & PhD Forum , Shanghai, 2012, pp. 449-453. doi: 10.1109/IPDPSW.2012.58.

- M. Ledwon, B. F. Cockburn and J. Han, “Design and Evaluation of an FPGA-based Hardware Accelerator for Deflate Data Decompression,” 2019 IEEE Canadian Conference of Electrical and Computer Engineering (CCECE) , Edmonton, AB, Canada, 2019, pp. 1-6. doi: 10.1109/CCECE.2019.8861851.

Cameron Collins is an undergraduate student (senior) at the University of Wisconsin at Green Bay (UWGB) pursuing a Bachelors in Computer Science with emphasis in Information Assurance and Security. His research interests focus on security issues in FPGAs, and he has worked on surveying security risks with FPGAs as part of his senior capstone research project under the supervision plus mentoring of Dr. Ankur Chattopadhyay. He has been working with the UWGB IT Support division as an employee and loves to explore IT issues as well as learn new technologies.

Dr. Ankur Chattopadhyay earned his Ph.D. in Computer Science from the University of Colorado at Colorado Springs (UCCS) , and is currently an Assistant Professor of Cybersecurity in the Computer Science Department at Northern Kentucky University (NKU) . He joined NKU in January, 2020, and his research interests include visual privacy, visual trust, computer science & cybersecurity education, privacy-enhancing computer vision & pattern recognition, adversarial thinking & learning in machine vision, and inclusive privacy & security in visual surveillance. He is currently an Editorial Board Member with the IEEE Future Directions Newsletter in Technology, Policy and Ethics . He is an active professional member of IEEE and ACM . He has over 30 peer-reviewed publications, including conference papers, newsletter articles and journal papers. He has more than 15 years of work experience in both academics and industry. Ankur is originally from Kolkata, India , where he did his Bachelors in Computer Engineering from the Institute of Engineering & Management (IEM) , and was employed with Tata Consultancy Services , a global computer consultancy firm, for almost 7 years. Before joining NKU, he was an Assistant Professor of Computer Science at the University of Wisconsin – Green Bay (UWGB) , where he founded and directed of the Center of Cybersecurity Education & Outreach. He was the principal investigator (PI) and the project director of the first-ever NSA/NSF GenCyber program in the state of Wisconsin at UWGB, where he has led and hosted the GenCyber program for three years. He has also worked with Google and Microsoft as the PI/project lead for the Google IgniteCS and Microsoft TechSpark grant programs at UWGB. His industry profile includes multiple roles like IT Analyst, Software Engineer and Embedded Systems Engineer.

Home | Contact & Support | Accessibility | Nondiscrimination Policy | IEEE Ethics Reporting | IEEE Privacy Policy | Terms © Copyright 2024 IEEE – All rights reserved. A not-for-profit organization, IEEE is the world's largest technical professional organization dedicated to advancing technology for the benefit of humanity.

fpga architecture Recently Published Documents

Total documents.

- Latest Documents

- Most Cited Documents

- Contributed Authors

- Related Sources

- Related Keywords

On-orbit real-time variational image destriping: FPGA architecture and implementation

Fpga architecture and design flow, distributed nonlinear-polynomial computing based on a group of polynomials over a galois field in the fpga architecture, research on machine learning optimization algorithm of cnn for fpga architecture, maple: a machine learning based aging-aware fpga architecture exploration framework, koios: a deep learning benchmark suite for fpga architecture and cad research, hardware software co-design based cpu-fpga architecture: overview and evaluation, unidirectional multi-bit fpga architecture for area efficient implementation of datapath circuits.

Field Programmable Gate Arrays (FPGAs) are increasingly being used to implement large datapath-oriented application that are designed to process multiple-bit wide data. Studies have shown that the regularity of these multi-bit signals can be effectively exploited to reduce the implementation area of datapath circuits on FPGAs that employ the traditional bidirectional routing. Most of modern FPGAs, however, employ unidirectional routing tracks which are more area and delay efficient. No study has investigated the design of multi-bit routing resources that can effectively transport multiple-bit wide signals using unidirectional routing tracks. This paper presents such an investigation of architectures which employ multi-bit connections and unidirectional routing resources to exploit datapath regularity. It is experimentally shown that unidirectional multi-bit architectures are 8.6% more area efficient than the conventional architecture. Additionally, this paper determines the most are efficient proportion of multi-bit connections.

The reduction of Crosstalk in VLSI due to parallel bus structure using Data Compression Bus Encoding technique implemented on Artix 7 FPGA Architecture

In this work, a bus encoding method is proposed that reduces the effect of crosstalk. The crosstalk usually occurs when the data is in parallel communicated. In planar structures, the crosstalk effect is large due to the usage of parallel communication and wide data patterns. In bus technique, the huge amount of wires is laid in equal over a significant time. One way to reduce crosstalk without changing the parallel communicating data lines is to reduce the wideband data patterns so as to reduce the power utilization. The proposed encoding method can minimize the crosstalk by reducing wide data patterns without degrading the performance. The architecture is implemented on Artix 7 FPGA at a 28nm technology node. The simulation is done using the HDL tool and the results are compared with the existing FPGA architecture. With the proposed method, the wire density and the power consumption are reduced by 57.4% and 50% respectively as compared with existing 45 nm technologies.

Export Citation Format

Share document.

A Survey of FPGA-Based Deep Learning Acceleration Research

- Conference paper

- First Online: 03 March 2022

- Cite this conference paper

- Ziyi Lv ORCID: orcid.org/0000-0002-9676-7833 40 , 41 &

- Jing Zhang ORCID: orcid.org/0000-0002-0171-0683 40 , 41

Part of the book series: Lecture Notes in Electrical Engineering ((LNEE,volume 813))

1984 Accesses

1 Citations

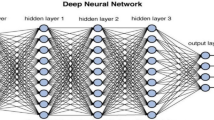

In a range of fields such as emotion detection, medical image processing and speech recognition, deep learning has recently achieved good results. With the pursuit of more precise results, many scholars try to add more new type network layers to increase the size of the neural network. However, this will lead to deeper and more intricate network models, and training and evaluating models requires intensive CPU calculations and tremendous computing resources which cannot be achieved by general purpose processors. Nowadays, some hardware accelerators such as Field Programmable Gate Array (FPGA) have been employed to accelerate the neural network, and FPGA with reconfigurability and low power consumption are currently applied to improve throughput of deep learning networks at a reasonable price. In this paper, the typical technologies and methods of accelerating deep learning network on FPGA in recent years are reviewed and analyzed with their advantages and disadvantages, and feasible research suggestions for the next research direction are given. It is expected that it will have a certain reference value for researchers in the field of deep learning acceleration and hardware optimization.

This is a preview of subscription content, log in via an institution to check access.

Access this chapter

- Available as PDF

- Read on any device

- Instant download

- Own it forever

- Available as EPUB and PDF

- Compact, lightweight edition

- Dispatched in 3 to 5 business days

- Free shipping worldwide - see info

- Durable hardcover edition

Tax calculation will be finalised at checkout

Purchases are for personal use only

Institutional subscriptions

Similar content being viewed by others

Optimizing Neural Networks for Efficient FPGA Implementation: A Survey

An Anatomization of FPGA-Based Neural Networks

A survey of FPGA-based accelerators for convolutional neural networks

Yann, L., Yoshua, B.: Convolutional networks for images, speech, and time series. Handb. Brain Theory Neural Netw. 3361 (10) (1995)

Google Scholar

Xingjian, S., Zhourong, C., Hao, W., et al.: Convolutional LSTM network. In: Proceedings of the 27th International Conference on Neural Information Processing Systems, A Machine Learning Approach for Precipitation Nowcasting, pp. 2672–2680. MIT Press (2015)

Ian, J.G., Jean, P.-A., Mehdi, M., et al.: Generative Adversarial Nets. MIT Press (2014)

Jiantao, Q., Song, S., Yu, W., et al.: Going deeper with embedded FPGA platform for convolutional neural network. In: Proceedings of the 2016 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays, pp. 26–35. ACM (2016)

Chen, Z., Peng, L., Sun, G., et al.: Optimizing FPGA-based accelerator design for deep convolutional neural networks. In: Proceedings of the 2015 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays, pp. 161–170. ACM (2015)

Williams, S., Waterman, A., Patterson, D.: Roofline: an insightful visual performance model for multicore architectures. Commun. Assoc. Comput. Mach. 52 (4), 65–76 (2009)

Xuelei, L., Liangkui, D., Li, W., Fang, C.: FPGA accelerates deep residual learning for image recognition. In: 2017 IEEE 2nd Information Technology, Networking, Electronic and Automation Control Conference (ITNEC). IEEE, Chengdu (2017)

Roberto, D., Griffin, L., Jasmina, V., Paul, C., Graham, T., Shawki, A.: Caffeinated FPGAs: FPGA framework for convolutional neural networks. In: 2016 International Conference on Field-Programmable Technology (FPT). IEEE, Xi’an (2017)

Chao, W., Junneng, Z., et al.: Hardware implementation on FPGA for task-level parallel dataflow execution engine. IEEE Trans. Parall. Distrib. Syst. 27 (8), 2303–2315 (2016)

Article Google Scholar

Chen, Z., Di, W., Jiayu, S., Guangyu, S., Guojie, L., Jason, C.: Energy-efficient CNN implementation on a deeply pipelined FPGA cluster. In: Proceedings of the 2016 International Symposium, pp. 326–331 (2016)

Hector A.G., Shahzad, M., Jerald, Y., Ibrahim M.E.: BioCNN: a hardware inference engine for EEG-based emotion detection. IEEE Access 140896–140914 (2020)

Lei, G., Chao, W., Xi, L., Huaping, C., Xuehai, Z.: MALOC: a fully pipelined FPGA accelerator for convolutional neural networks with all layers mapped on chip. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 37 (11), 2601–2612 (2018)

Ming, X., Zunkai, H., Li, T., Hui, W., Victor, C., Yongxin, Z., Songlin, F.: SparkNoC: an energy-efficiency FPGA-based accelerator using optimized lightweight CNN for edge computing. J. Syst. Archit. 115 (4), 101991 (2021)

Gan, F., Zuyi, H., Song, C., Feng, W.: Energy-efficient and high-throughput FPGA-based accelerator for Convolutional Neural Networks. In: 2016 13th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT). IEEE, Hangzhou (2017)

Dong, W., An, J., Xu, K.: PipeCNN: an OpenCL-based FPGA accelerator for large-scale convolution neuron networks. CoRR 1611 (02450) (2016)

Kaiyuan, G., Lingzhi, S., Jiantao, Q., et al.: Angel-eye: a complete design flow for mapping CNN onto embedded FPGA. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 37 (1), 35–47 (2017)

Liqiang, L., Yun, L., Qingcheng, X., Shengen, Y.: Evaluating fast algorithms for convolutional neural networks on FPGAs. In: 2017 IEEE 25th Annual International Symposium on Field-programmable Custom Computing Machines. IEEE, Napa (2017)

Yufei, M., Yu, C., Sarma, V., Jae-sun, S.: Optimizing the convolution operation to accelerate deep neural networks on FPGA. IEEE Trans. Very Large-Scale Integr. (VLSI) Syst. 26 (7), 1354–1367 (2018)

Lei, G., Chao, W., Xi, L., Huangping, C., Xuehai, Z.: A power-efficient and high-performance FPGA accelerator for convolutional neural networks. In: Proceedings of the 12th IEEE/ACM/IFIP International Conference on Hardware/Software Codesign and System Synthesis Companion, pp. 1–2 (2017)

Chao, H., Siyu, N., Gengsheng, C.: A layer-based structured design of CNN on FPGA. In: 2017 IEEE 12th International Conference on ASIC (ASICON). IEEE, Guiyang (2017)

Waichi, F., Kaiyen, W., Nicolas, F., Yunlun, H., Yude, H.: Development and validation of an EEG-based real-time emotion recognition system using edge AI computing platform with convolutional neural network system-on-chip design. IEEE J. Emerg. Sel. Top. Circ. Syst. 9 (4), 645–657 (2019)

Jing, M., Chen, L., Zhiyong, G.: Hardware Implementation and optimization of tiny-YOLO network. Springer, Singapore (2017)

Ke, X., Xiaoyun, W., Dong, W.: A scalable OpenCL-based FPGA accelerator for YOLOv2. In: 2019 IEEE 27th Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM). IEEE, San Diego (2019)

Hiroki, N., Masayuki, S., Shimpei, S.: A demonstration of FPGA-based you only look once version2 (YOLOv2). In: 2018 28th International Conference on Field Programmable Logic and Applications (FPL). IEEE, Dublin (2018)

Hiroki, N., Haruyoshi, Y., Tomoya, F., Shimpei, S.: A lightweight YOLOv2: a binarized CNN with a parallel support vector regression for an FPGA. In: Proceedings of the 2018 ACM/SIGDA International Symposium, pp. 31–40. ACM (2018)

Chaoyang, Z., Kejie, H., Shuyuan, Y., Ziqi, Z., Hejia, Z., Haibin, S.: An efficient hardware accelerator for structured sparse convolutional neural networks on FPGAs. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 1–13 (2020)

Zixiao, W., Ke, X., Shuaixiao, W., Li, Liu., Lingzhi, L., Dong, W.: Sparse-YOLO: hardware/software co-design of an FPGA accelerator for YOLOv2. IEEE Access 8 (99), 116569–116585 (2020)

Xianchao, X., Brian, L.: FCLNN: a flexible framework for fast CNN prototyping on FPGA with OpenCL and Caffe. In: 2018 International Conference on Field-Programmable Technology (FPT). IEEE, Naha (2018)

Caiwen, D., Shuo, W., Ning, L., Kaidi, X., Yanzhi, W., Yun, L.: REQ-YOLO: a resource-aware, efficient quantization framework for object detection on FPGAs. In: Proceedings of the 2019 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays, pp. 33–42 (2019)

Download references

Acknowledgements

This research is supported by: (1) 2020-2022 National Natural Science Foundation of China under Grand (Youth) No. 52001039 (2) 2020-2022 Funding of Shandong Natural Science Foundation in China No. ZR2019LZH005.

Author information

Authors and affiliations.

School of Information Science and Engineering, University of Jinan, Jinan, 250022, China

Ziyi Lv & Jing Zhang

Shandong Provincial Key Laboratory of Network-Based Intelligent Computing, Jinan, 250022, China

You can also search for this author in PubMed Google Scholar

Corresponding author

Correspondence to Jing Zhang .

Editor information

Editors and affiliations.

School of Remote Sensing and Information Engineering, Wuhan University, Wuhan, Hubei, China

Department of Computer Science, University of Alabama, Tuscaloosa, AL, USA

National University of Defense Technology, Changsha, Hunan, China

Big Data Institute, Hunan University of Finance and Economics, Changsha, Hunan, China

Rights and permissions

Reprints and permissions

Copyright information

© 2022 The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper.

Lv, Z., Zhang, J. (2022). A Survey of FPGA-Based Deep Learning Acceleration Research. In: Yao, J., Xiao, Y., You, P., Sun, G. (eds) The International Conference on Image, Vision and Intelligent Systems (ICIVIS 2021). Lecture Notes in Electrical Engineering, vol 813. Springer, Singapore. https://doi.org/10.1007/978-981-16-6963-7_5

Download citation

DOI : https://doi.org/10.1007/978-981-16-6963-7_5

Published : 03 March 2022

Publisher Name : Springer, Singapore

Print ISBN : 978-981-16-6962-0

Online ISBN : 978-981-16-6963-7

eBook Packages : Engineering Engineering (R0)

Share this paper

Anyone you share the following link with will be able to read this content:

Sorry, a shareable link is not currently available for this article.

Provided by the Springer Nature SharedIt content-sharing initiative

- Publish with us

Policies and ethics

- Find a journal

- Track your research

fpga IEEE PAPER 2018

Free ieee paper and projects, ieee projects 2022, seminar reports, free ieee projects ieee papers.

IMAGES

VIDEO

COMMENTS

Since their inception more than thirty years ago, field-programmable gate arrays (FPGAs) have been widely used to implement a myriad of applications from different domains. As a result of their low-level hardware reconfigurability, FPGAs have much faster design cycles and lower development costs compared to custom-designed chips. The design of an FPGA architecture involves many different ...

In IEEE International Parallel and Distributed Processing Symposium Workshops (IPDPSW). IEEE, 168 - 171. Google Scholar [102] Mbongue Joel Mandebi, Saha Sujan Kumar, and Bobda Christophe. 2021. A security architecture for domain isolation in multi-tenant cloud FPGAs. In IEEE Computer Society Annual Symposium on VLSI (ISVLSI). IEEE, 290 - 295.

Reconfigurable computing is a potential paradigm which has been effectively performing mostly in the developments of devices likely Field Programmable Gate Arrays (FPGAs). This paper illustrates the reconfigurable architecture of FPGA and its types. Most widely used high-speed computation fabrics utilized in reconfigurable computing are FPGAs. This paper demonstrates the architectures used in ...

Feature papers represent the most advanced research with significant potential for high impact in the field. ... This part we research four kinds of platforms—FPGA, GPU, ASIC and MCU. ... Current trends, cross-layer optimizations, and open research challenges. In Proceedings of the 2019 IEEE Computer Society Annual Symposium on VLSI (ISVLSI ...

We present an overview of the most relevant DNN architectures that have been the focus of research for hardware acceleration during the last years (Section 2).Correspondingly, we highlight key FPGA features and explain their specific suitability for DNN acceleration (Section 3).. We detail recent DNN acceleration strategies and highlight their influence on an FPGA-based DNN inference ...

FPGA-based Accelerators of Deep ... SADIQ M. SAIT1, 2, (Senior Member, IEEE), AND AIMAN EL-MALEH , (Member, IEEE) 1Department of Computer Engineering, King Fahd University of Petroleum & Minerals, Dhahran-31261, Saudi Arabia 2Center for Communications and IT Research, Research Institute, King Fahd University of Petroleum & Minerals ...

Current Trends and Future Directions in Security of FPGA Applications with Focus on Thin Clients. Cameron Collins, University of Wisconsin - Green Bay and Ankur Chattopadhyay, Northern Kentucky University March 2020. 1. Introduction. Recent high-profile security flaws in conventional desktop and server processors have brought increased interest and attention to the risks posed by proprietary ...

Abstract. FPGAs are currently the most suitable hardware accelerators to implement and accommodate the non-stop growth of machine learning applications. This paper presents an FPGA architecture with added posit multipliers that outweigh the current IEEE-754 multipliers in terms of delay and area. Since machine learning algorithms involve a lot ...

In this manuscript, we present a survey of designs and implementations of research sensor nodes that rely on FPGAs, either based upon standalone platforms or as a combination of microcontroller and FPGA. Several current challenges in sensor networks are distinguished and linked to the features of modern FPGAs. As it turns out, low-power optimized FPGAs are able to enhance the computation of ...

The proposed research work describes an FPGA implementation of IEEE 1588 Precision Time Protocol (PTP) that exploits the CERN Timing, Trigger and Control (TTC) system as a multicast messaging ...

Design and development of maximum power point tracking algorithm using field programmable gate array. Implementation of Digital PID controller in Field Programmable Gate Array (FPGA) A super-serial Galois fields multiplier for FPGAs and its application to public-key algorithms. Multichannel High-Speed Fiber Bragg Grating Interrogation System ...

Feature papers represent the most advanced research with significant potential for high impact in the field. ... steps, its use is very restricted to very specific applications, as its design effort is quite high. On the other side, IEEE-754 floating-point may have resolution problems in case of the 32-bit version, and excessive hardware usage ...

Field Programmable Gate Arrays (FPGAs) are increasingly being used to implement large datapath-oriented application that are designed to process multiple-bit wide data. Studies have shown that the regularity of these multi-bit signals can be effectively exploited to reduce the implementation area of datapath circuits on FPGAs that employ the ...

Field-programmable gate arrays (FPGA's) are now widely used for the implementation of digital systems, and many commercial architectures are available. A... The design of a SRAM-based field-programmable gate array—part II: circuit design and layout: IEEE Transactions on Very Large Scale Integration (VLSI) Systems: Vol 7, No 3

3 The Current Status of Deep Learning Acceleration. In this section, the latest technologies of FPGA for accelerating and optimizing network algorithms in deep learning research, such as emotion detection and target detection, are reviewed. In the field of emotion detection, Hector et al. [ 11] proposed BioCNN, an EEG-based biological neural ...

Ieee Research Papers on Fpga - Free download as PDF File (.pdf), Text File (.txt) or read online for free. ieee research papers on fpga

fpga IEEE PAPER 2018. ABSTRACT This work aims to design and implement a digital flight controller on a FPGA prototype board for stabilizing a Quadcopter unmanned aerial vehicle (UAV). The purpose of the project was to access the feasibility of using an FPGA in the stabilized control of an.